### INTRODUCTION TO

### **CARVER MEAD • LYNN CONWAY**

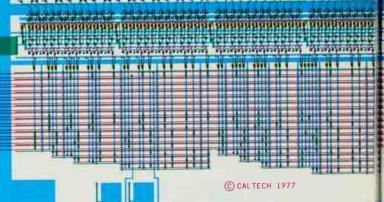

### - 11 T alaystata salata calata sal abaratatatatatatatatatatat KAR AANAAAA Ing a second second

fin fin fin fin fin fin fin fin fin sin fin sin fin sin fin New Sector Sector Sector Salar Sher the Sher Sher Sher She a har blitter ar What fense ins enterns enterns enterns enterns enterns enterns enterns The further for the flat for the state of th and the second second they white in Constant on Constant in Constant in Constant in Const Superior Superior Superior Superior Superior Superior Superior Fit Willing Willing Willinger No ite de la static de de de la de la de la de la nstat at at attact at tal at tal as taking a said

S. Ambaconnar

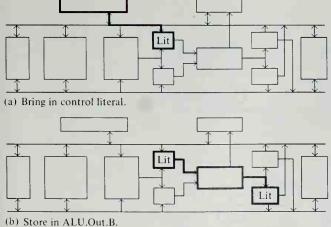

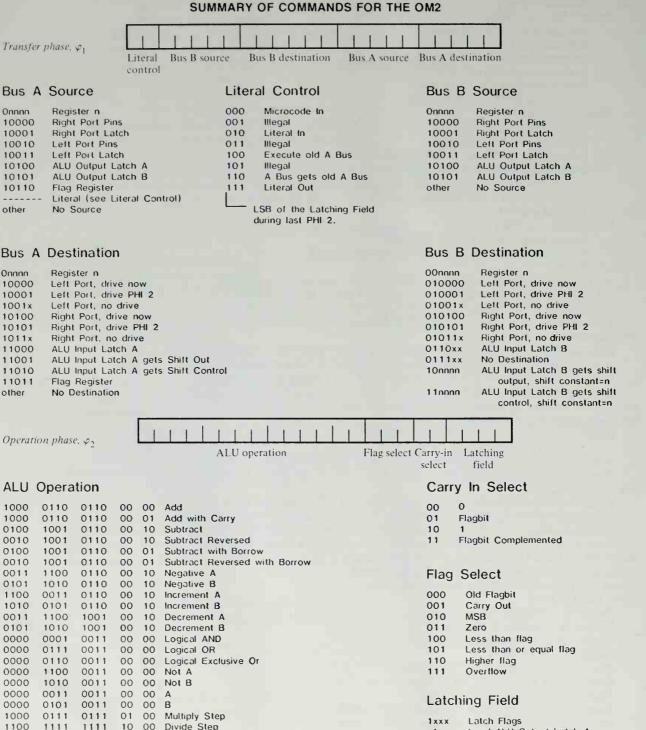

### Digitized by the Internet Archive in 2011

http://www.archive.org/details/introductiontovl00mead

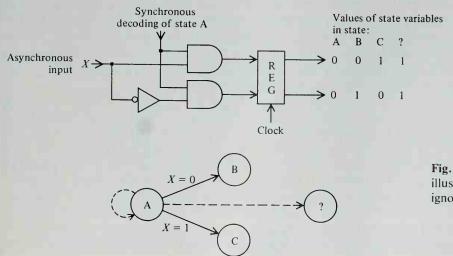

# INTRODUCTION TO

### CARVER MEAD

Professor of Computer Science, Electrical Engineering, and Applied Physics, California Institute of Technology

### LYNN CONWAY

Research Fellow, and Manager, VLSI System Design Area Palo Alto Research Center, Xerox Corporation

### **v**v

ASIN'S LOUIS CONTRACTOR

Reading, Massachusetts • Menlo Park, California London • Amsterdam • Don Mills, Ontario • Sydney

ADDISON-WESLEY PUBLISHING COMPANY

### This book is in the Addison-Wesley Series in Computer Science

Consulting Editor Michael A. Harrison

### Library of Congress Cataloging in Publication Data

Mead, Carver A Introduction to VLSI systems.

Integrated circuits—Large scale integration.

Microcomputers.

Digital electronics.

Computer architecture.

Conway, Lynn A., joint author.

Title.

TK7874.M37

621.3819'535

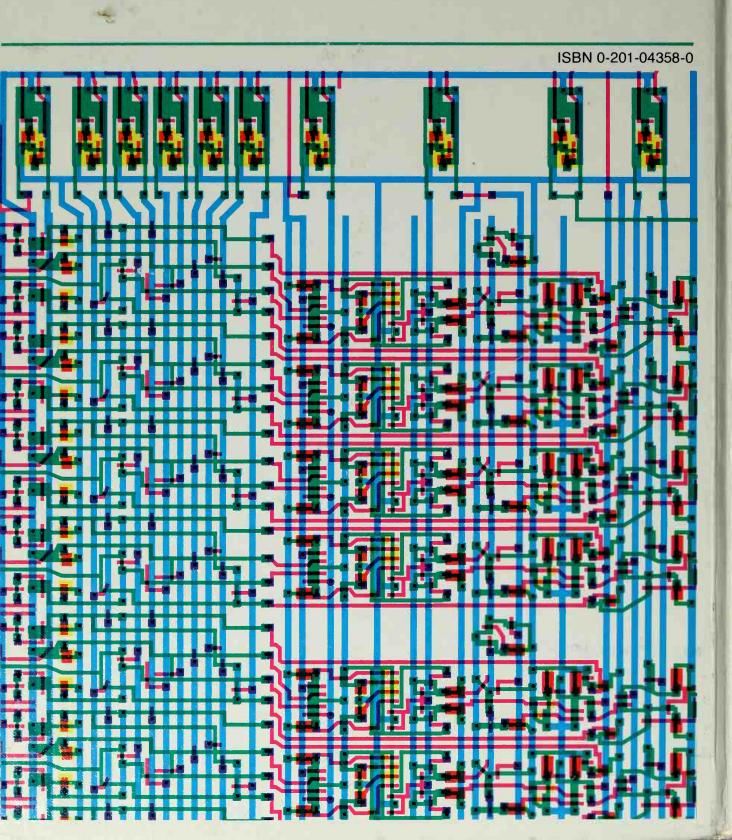

ISBN 0-201-04358-0

### Second printing, October 1980

Copyright © 1980 by Addison-Wesley Publishing Company, Inc. Philippines copyright 1980 by Addison-Wesley Publishing Company, Inc.

78-74688

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada. Library of Congress Catalog Card No. 78-74688.

ISBN 0-201-04358-0 KLMNOP-HA-898765

### TO W. R. SUTHERLAND

### PREFACE

As a result of improvements in fabrication technology, Large Scale Integrated (LSI) electronic circuitry has become so dense that a single silicon LSI chip may contain tens of thousands of transistors. Many LSI chips, such as microprocessors, now consist of multiple complex subsystems, and thus are really *integrated systems* rather than integrated circuits.

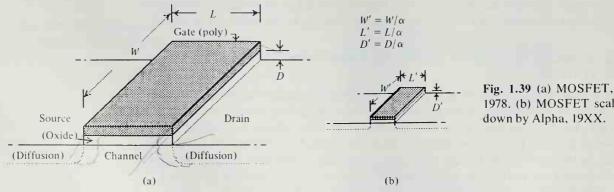

What we have seen so far is only the beginning. Achievable circuit density now doubles with each passing year or two. Physical principles indicate that transistors can be scaled down to less than 1/100th of their present area and still function as the sort of switching elements with which we can build digital systems. By the late 1980s it will be possible to fabricate chips containing millions of transistors. The devices and interconnections in such very large scale integrated (VLSI) systems will have linear dimensions smaller than the wavelength of visible light. New high-resolution lithographic techniques have already been demonstrated that will enable fabrication of such circuitry.

VLSI electronics presents a challenge, not only to those involved in the development of fabrication technology, but also to computer scientists and computer architects. The ways in which digital systems are structured, the procedures used to design them, the trade-offs between hardware and software, and the design of computational algorithms will all be greatly affected by the coming changes in integrated electronics. We believe this will be a major area of activity in computer science on through the 1980s.

Until recently the design of integrated circuitry has been the province of circuit and logic designers working within semiconductor firms. Computer architects have traditionally composed systems from standard integrated circuits designed and manufactured by these firms but have seldom participated in the specification and design of these circuits. Electrical Engineering and Computer Science (EE/CS) curricula reflect this tradition, with courses in device physics and integrated circuit design aimed at a different group of students than those interested in digital system architecture and computer science.

This text is written to fill a current gap in the literature and to introduce all EE/CS students to integrated system architecture and design. Combined with individual study in related research areas and participation in large system design projects, this text provides the basis for a graduate course-sequence in integrated systems. However, it is primarily intended for use in intensive undergraduate courses on the subject. The material can also be used to augment courses on computer architecture. We assume the reader's background contains the equivalent of introductory courses in computer science, electronic circuits, and digital design.

There have been major obstacles in the way of those seeking an overall understanding of integrated systems. Integrated electronics has developed in a heatedly competitive and often secretive business environment. There has been a proliferation of different device technologies, circuit design families, logic design techniques, maskmaking and wafer fabrication techniques, etc. Many of these technologies have sprung up from the grass roots of "Silicon Valley" in the San Francisco Bay Area of California, and thus many of the "experts" are located in that one region. Most workers in the industry have concentrated on narrow specialties. Separate integrated electronics cultures have independently evolved within many companies, and thus the terminology and practices of the specialties vary from company to company.

As a result of this background, texts on integrated electronics have tended to give detailed accounts of some very narrow horizontal segment of the overall subject, such as device physics or circuit design, and are often tied in subtle ways to some specific context, thus limiting their general applicability.

We have chosen instead to provide just enough essential information about devices, circuits, fabrication technology, logic design techniques, and system architecture to enable the reader to fully span the entire range of abstractions from the underlying physics to complete VLSI digital computer systems. A rather small set of key concepts is sufficient. Only by learning the essence of each topic, and by carrying along the least amount of mental baggage at each step, will the student emerge with a good overall understanding of the subject. This understanding can then be mapped into the reader's own space of application, technology, and technical culture.

The high rate of change of integrated electronics presents another obstacle: information often becomes obsolete very rapidly. The major force for obsolescence is the ongoing improvement in fabrication technology, leading to smaller and smaller devices as time passes and thus to a constant change in device characteristics. We attack this obstacle by stressing the effects of the scalingdown of device dimensions. Many of the coming changes in system architectural parameters are thus anticipated. The reader will learn what is common to systems composed of 6  $\mu$ m, 2  $\mu$ m, and 0.5  $\mu$ m devices, and what is not.

While the material in this text is presented in a particular order, it need not be read in that order. Each chapter presents material from a distinct level in the hierarchy of disciplines involved in integrated systems. The material falls into four major groupings: Chapters 1 and 2 provide the basics of devices, circuits, and fabrication; Chapters 3 and 4 give the basics of system design and implementation; Chapters 5 and 6 present an example of LSI system design: topics of current research interest are discussed in Chapters 7, 8, and 9. We recommend that readers start in the chapter where they are most knowledgeable, and read until information is required from an adjacent area described in some other chapter. By using this algorithm and consulting the suggested references where necessary, readers can gradually work through the primary material of all chapters. Although much of the material in this text is previously unpublished, it nevertheless contains only basic concepts. However, these concepts cover quite a wide range of disciplines and are easily visualized only after the overall context becomes clear.

In any given technology, form follows function in a particular way. The most efficient first step towards understanding the architectural possibilities of a technology is the study of carefully selected existing designs. However, system architecture and design, like any art, can only be learned by doing. Carrying a small design from conception through to successful completion provides the confidence necessary to undertake larger designs. The space of possibilities unfolds only as the medium is worked. This book provides a set of selected design examples and also describes procedures for implementing one's own designs. Because of the density, speed, and topological properties of *n*MOS, and the easy access to *n*MOS wafer fabrication, that technology is used for our examples. The architectural skill of mapping function into form, when once acquired, can then be extended to other technologies.

The general availability of courses in VLSI system design at major universities marks the beginning of a new era in electronics. The rate of systems innovation using this remarkable technology need no longer be limited by the perceptions of a handful of semiconductor companies and large computer manufacturers. New metaphors for computation, new design methodologies, and an abundance of new application areas are already arising within the universities, within many system firms, and within a multitude of new small enterprises. There may never have been a greater opportunity for free enterprise than that presented by these circumstances.

An atmosphere of excitement and anticipation pervades this field. A growing community of workers from many backgrounds, computer scientists, electrical engineers, mathematicians, and physicists are collaborating on a common problem area that has not yet become classical. The territory is vast, and largely unexplored. The rewards are great for those who simply press forward.

Pasadena, California Belmont, California July 1979 C.M. L.C.

### BACKGROUND

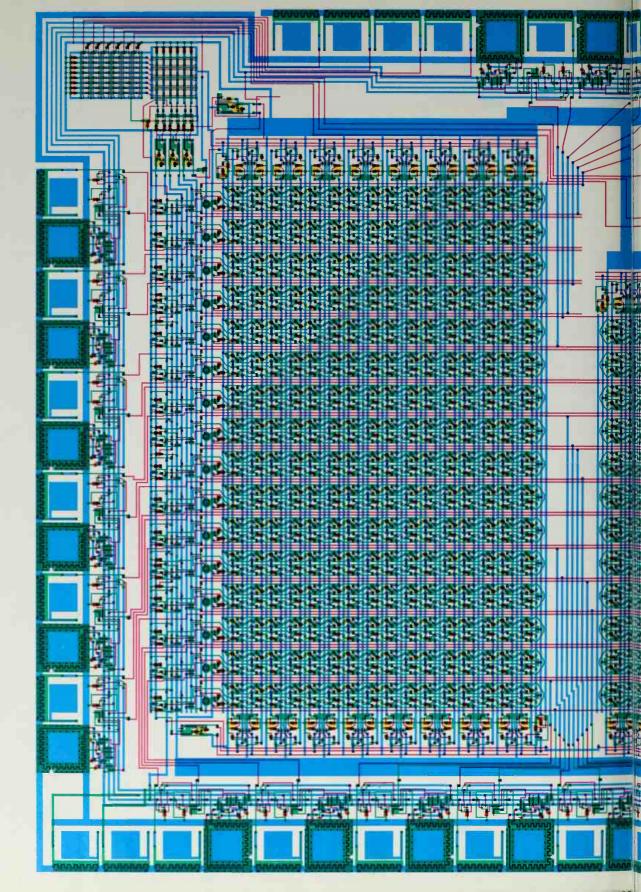

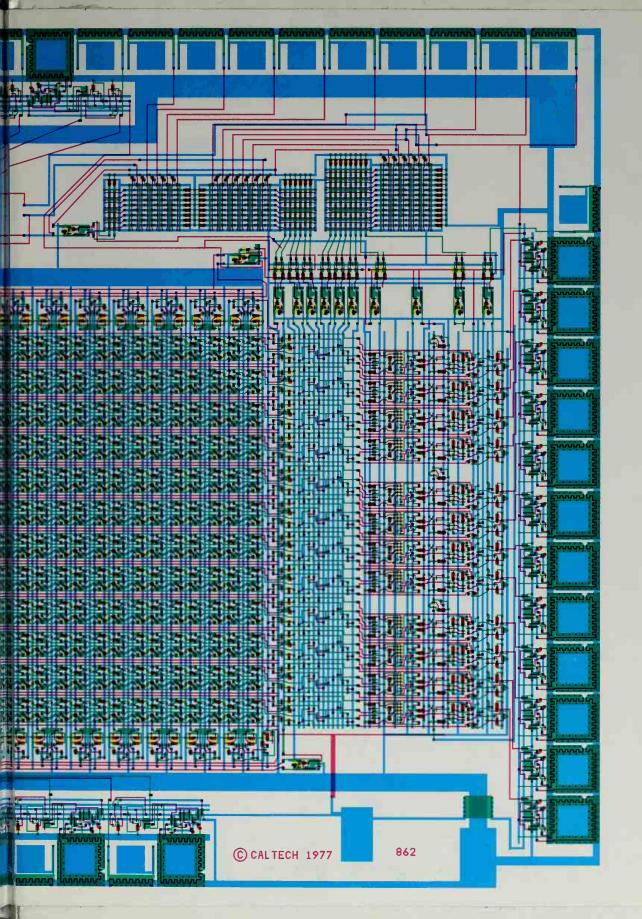

This text has its origins in a series of courses in integrated circuit design given by Carver Mead at Caltech, beginning in 1970. Starting in 1971, students in these courses designed and debugged their own integrated circuits. The students undertook increasingly complex system designs, using only rather simple implementation aids. The structured design methodology presented in this text has evolved within this milieu. These early courses greatly benefited from interactions with friends in industry, particularly Robert Noyce, Gordon Moore, Frederico Faggin, Dov Frohman-Bentchkowsky, Ted Jenkins, and Joel Sorem.

A separate Computer Science activity was created at Caltech in 1976, with integrated systems as a focus. An early, informal association was formed with systems architects in industry, in particular with the then newly formed LSI Systems Area, led by Lynn Conway, at Xerox Palo Alto Research Center (PARC). The increased interaction of Caltech students and faculty with industrial researchers stimulated the research on both sides.

Work on this text began in August 1977. Collaborators from a number of universities and industrial firms joined in the enterprise. Prior to commercial publication, several limited printings were distributed to a selected group of universities as notes for courses on integrated systems. The first three chapters were used as course notes during the fall of 1977, in courses given by Carver Mead at Caltech and by Carlo Séquin at U.C. Berkeley. The first five chapters were used during the spring of 1978 in courses given by Ivan Sutherland and Amr Mohsen at Caltech, by Robert Sproull at Carnegie-Mellon University, by Dov Frohman-Bentchkowsky at Hebrew University, Jerusalem, and by Fred Rosenberger at Washington University, St. Louis. The third and final prepublication printing of all nine chapters, in the fall of 1978, was used in the courses at Caltech and U.C. Berkeley, and in new courses by Kent Smith at the University of Utah, and by Lynn Conway, while visiting at M.I.T.

The 1978 M.I.T. course provided a final test, prior to publication of this text, to confirm the transportability of the project-oriented form of the course (in which as much emphasis is placed on creative architectural activity as on formal analysis), and to also confirm the technical and economic feasibility of the remote-entry of student LS1 designs to a central facility for fast-turnaround implementation. In the future, M.I.T. will offer this as course 6.371, with Jonathan Allen teaching it in the fall of 1979.

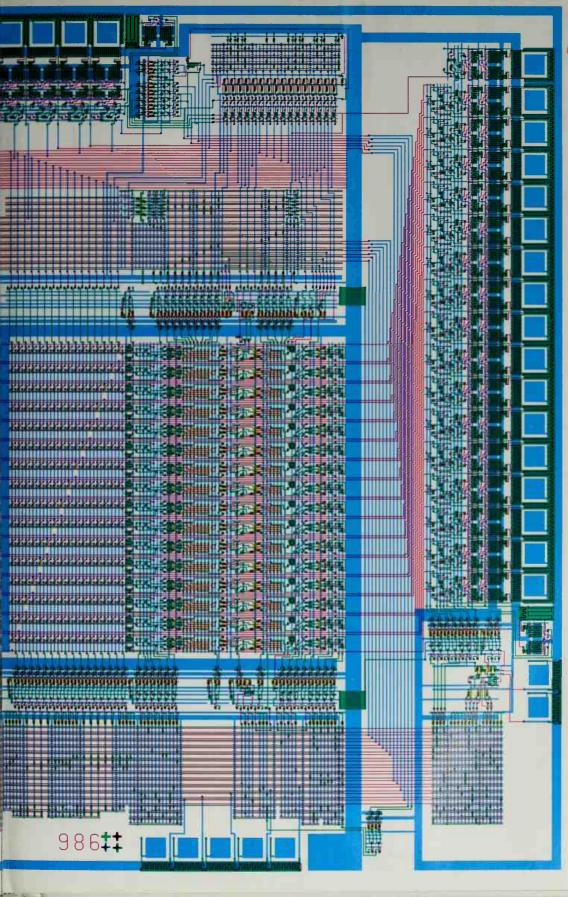

The following information concerning the M.1.T. experience may be useful to those planning similar activities. The course began in mid-September and was attended by 30 students (mostly graduate EE/CS students). Most of the formal lecture material necessary for undertaking projects (covering selected portions of Chapters 1 through 6 of this text) was completed by early November. The students then defined and began work on their LSI design projects. A design cut-off date of December 5 was set, and most designs were completed by that time. The projects included a LISP Microprocessor, a Graphics Memory Subsystem for mirroring and rotating bit-map data, a Writeable PLA project, the Data Path for a Bit-Slice Microprocessor, an LRU Virtual-Memory Paging subsystem, a Bus-Interfaceable Real-Time Clock-Calendar, a Multifunction Smart Memory, several digital signal-processing projects, several subsystems for data-base operations, and many other innovative designs.

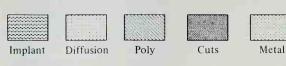

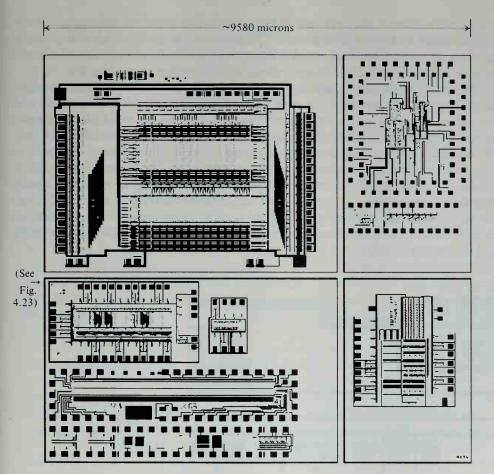

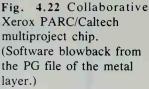

Students described their layouts in a simple subset of CIF2.0, using a standard text-editor running on a DEC-20. The only hardware added to the DEC-20 system to support the course were several CRT terminals, two HP four-color pen plotters, and a connection to the local ARPANET host machine. The only software developed were programs for parsing the CIF subset, for instantiating data for plotting, and for driving the plotters. A small library of useful cells, namely input pads with lightning arrestors, output pads with cascaded drivers, and a set of PLA cells, were made available in CIF form. Some students developed their own symbolic layout languages and translaters to CIF, in order to make layout encoding less tedious. By using a structured design methodology the students were able to complete substantial LSI projects in a short period of time, using only primitive design tools. Each project contained on the order of several hundred to several thousand transistors. The logistics of interacting with the large group of student designers to organize the multiproject chip (updating the rules of the game, selecting projects for inclusion, negotiating space allocations, answering individual questions, etc.) were expedited by using the message system on the DEC-20. The corresponding interactions with the remote implementation facility (PARC) were handled via electronic mail.

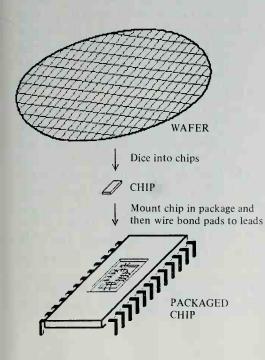

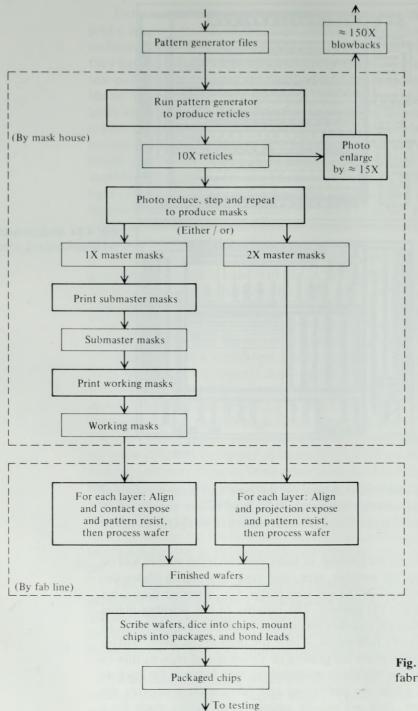

On December 6, 1978, the individual CIF2.0 design files were transmitted from M.I.T. via the ARPANET to Xerox PARC. This was an additional test by these ARPA contractors of the use of such packet-switching networks for transmitting LSI design files and organizing multiproject chip sets. At PARC all the student designs were merged into a multiproject chip design file, from which masks were generated using Micro Mask, Inc.'s electron-beam maskmaking facility. Wafers were fabricated at Hewlett-Packard's Deer Creek Laboratory, which cooperated in the feasibility test. The wafers were returned to M.I.T. and electrically characterized by tests of the project-set electrical test patterns. They were then diced and the resulting chips packaged. Packaged chips, with wire-bonding customized for each project, were made available to all students by January 18, 1979. Many of the projects have since undergone thorough functional testing by the students. A number of these function completely correctly. Most exhibited only minor bugs, typically at the logic level of abstraction, of a sort reminiscent of one's first efforts at constructing large programs in a new language.

As a common VLSI system design culture spreads, as higher-level design aids are developed and shared within this culture, and as standard-interface commercially-accessible implementation facilities are established, we will undoubtedly see far more ambitious courses, projects, and research activities undertaken by students and faculty within the universities. And thus the period of exploration begins.

### ACKNOWLEDGEMENTS

We wish to express our gratitude to the many individuals who have contributed their ideas, their time, and their energy toward the creation of this textbook. In particular, we wish to thank the following:

For contributions to the text: Chuck Seitz, California Institute of Technology, for contributing Chapter 7, System Timing, to the text; Martin Rem, Eindhoven University of Technology, and Sally Browning, Caltech, for their contributions to Chapter 8; David Johannsen, Caltech, for his major contributions to Chapters 5 and 6; H. T. Kung and Charles Leiserson, Carnegie-Mellon University, for permission to reprint their original, copyrighted work, Algorithms for VLSI Processor Arrays, as Section 3 of Chapter 8: Robert Sproull, CMU, and Richard Lyon, Xerox PARC, for the CIF section; Carlo Séquin, U.C. Berkeley, for his contributions to Chapter 1, his detailed review of the text, and his many suggestions for improvements; John Best, Chuck Seitz, Jim Kajiya, and Tom McGill, Caltech, and Johan de Kleer, Xerox PARC, for their stimulating discussions and suggestions for Chapter 9; Robert Sproull and Wayne Wilner, for their assistance in the preparation of Chapter 8; Hank Smith, M.I.T., for his contributions to the section on high-resolution lithography; Douglas Fairbairn, Xerox PARC, and James Rowson, Caltech, for the ICARUS section; Dale Green and Liz Bond, Xerox EOS, for technical assistance in the preparation of the text, figures, and color plates; Barbara Baird of Xerox PARC, for overseeing the printing and distribution of the prepublication versions of the text.

For valuable discussions and comments: Robert Sproull; Fred Rosenberger and Charles Molnar, Washington University; Richard Lyon, Doug Fairbairn, Wayne Wilner, and Leo Guibas, Xerox PARC; Chuck Seitz and Ivan Sutherland,

### xii Acknowledgements

Caltech; Craig Mudge, DEC; Bill Heller, IBM; Gerry Parker, Dick Pashley, and John Wipfli, Intel; Harry Peterson, BNR Ltd.; Al Perlis, Yale University; Wesley Clark.

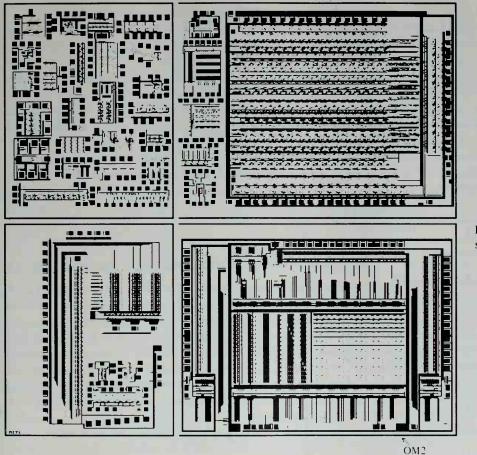

For participation in the OM projects: Dave Johannsen, Mike Tolle, Chris Carroll, Rod Masumoto, Ivan Sutherland, Chuck Seitz, Danny Cohen, and Leslie Froisland.

For helping to establish the multiproject chip capability: Richard Lyon, Doug Fairbairn, and Alan Bell, Xerox PARC; Bob Hon, CMU; Carlo Séquin, U.C. Berkeley; Ted Jenkins, Intel; Jim Rowson, Ron Ayres, and Steve Trimberger, Caltech.

For contributions to the M.I.T. 1978 VLSI design course: Jonathan Allen, Paul Penfield, Jr., Paul E. Gray, Fernando Corbató, Bill Henke, Glen Miranker, Joy Thompson, Dimitri Antoniadis, Stephen Senturia, Gerald Sussman, Jack Holloway, and Tom Knight, M.I.T.; Robert Noyce and Gordon Moore, Intel Corporation; Merrill Brooksby, and Patricia Castro, Hewlett-Packard; Richard Lyon and Alan Bell, Xerox PARC; and, especially, all the students who participated in course 6.978.

For long-standing support of integrated systems research at Caltech: The Office of Naval Research; Robert Noyce and Gordon Moore, Intel Corporation.

We are very grateful to Xerox Corporation for providing us access to the *Alto-Ethernet-Dover* research-prototype office systems at Xerox PARC and elsewhere within Xerox. Throughout the development of the ideas for this textbook, these personal, distributed computer systems enabled a large, scattered group of collaborators to function as a closely knit research community. These systems also enabled rapid creation and distribution of the prepublication printings of the text, thus helping us obtain valuable feedback from those teaching the early courses in the universities.

We are especially grateful to W. R. Sutherland, Manager, Systems Science Laboratory of Xerox PARC, for providing us with inspiration, guidance, and support; to Ivan Sutherland, Fletcher Jones Professor of Computer Science, Caltech, for his role in starting the Computer Science activities at Caltech, and for establishing links between the computer science community and the emerging activities in integrated systems; to Robert E. Kahn, Chief Scientist and Director for Information Processing Techniques, Defense Advanced Research Projects Agency, for encouraging and supporting integrated systems research in the universities; and to George E. Pake, Vice-President, Xerox Corporate Research, for creating the research environment that made this book possible.

### MOS DEVICES AND CIRCUITS 1 1.1 The MOS transistor 1 1.2 The basic inverter 5 1.3 Inverter delay 10 1.4 Parasitic effects 11 1.5 Driving large capacitive loads 12 1.6 Space versus time 14 1.7 Basic NAND and NOR logic circuits 15 1.8 Super buffers 17 1.9 A closer look at the electrical parameters 18 1.10 Depletion mode pull-ups versus enhancement mode pull-ups 20 1.11 Delays in another form of logic circuitry 22 1.12 Pull-up/pull-down ratios for inverting logic coupled by pass transistors 24 1.13 Transit times and clock periods 25 1.14 Properties of cross-coupled circuits 26 1.15 A fluid model for visualizing MOS transistor behavior 29 1.16 Effects of scaling down the dimensions of MOS circuits and systems 33

CONTENTS

2

1

38

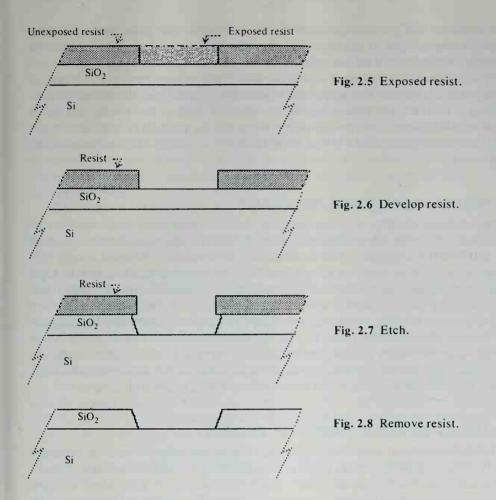

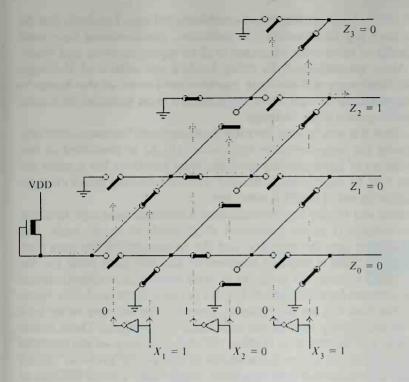

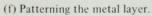

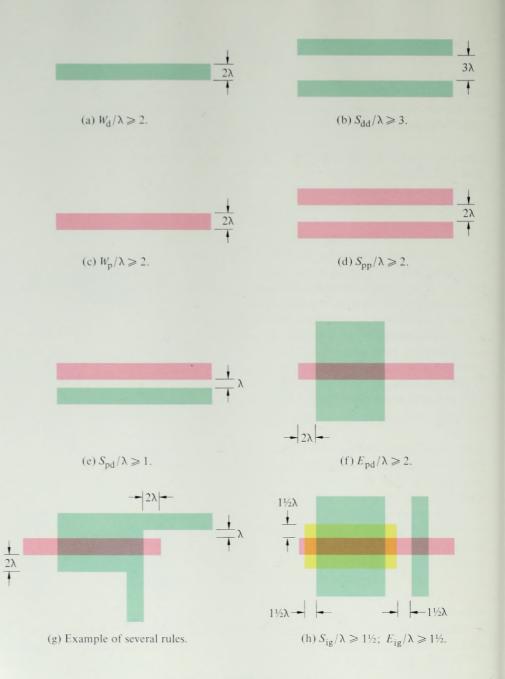

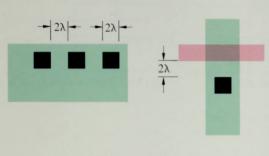

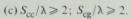

| 2.1 | Patterning                                     | 39 |

|-----|------------------------------------------------|----|

| 2.2 | Scaling of patterning technology               | 42 |

| 2.3 | The silicon gate <i>n</i> -channel MOS process | 42 |

| 2.4 | Yield statistics                               | 45 |

| 2.5 | Scaling of the processing technology           | 46 |

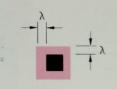

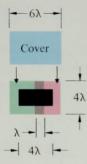

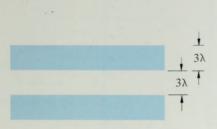

| 2.6 | Design rules                                   | 47 |

| 2.7 | Electrical parameters                          | 51 |

INTEGRATED SYSTEM FABRICATION

| 2.8  | Current limitations in conductors | 52 |

|------|-----------------------------------|----|

| 2.9  | A closer look at some details     | 53 |

| 2.10 | Choice of technology              | 56 |

| DATA AND CONTROL FLOW IN SYSTEMATIC STRUCTURES | S 60 |

|------------------------------------------------|------|

| 3.1 Introduction                               | 60   |

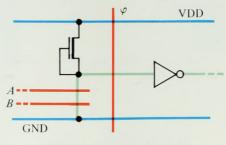

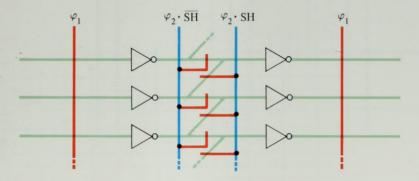

| 3.2 Notation                                   | 64   |

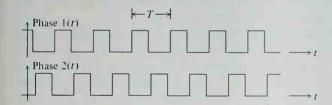

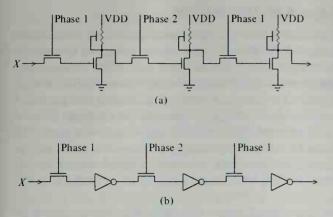

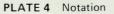

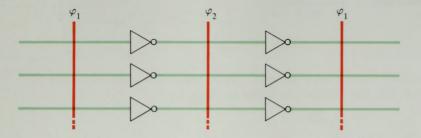

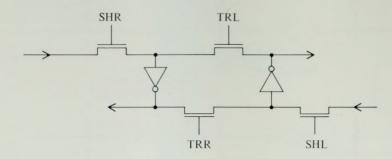

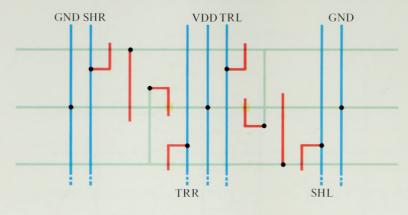

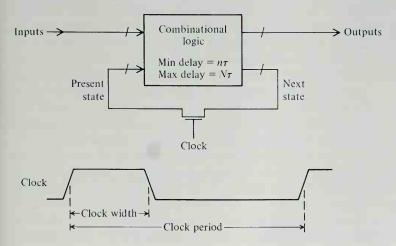

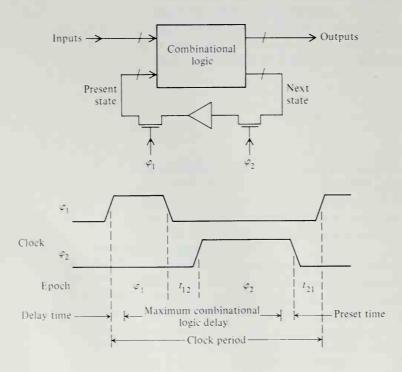

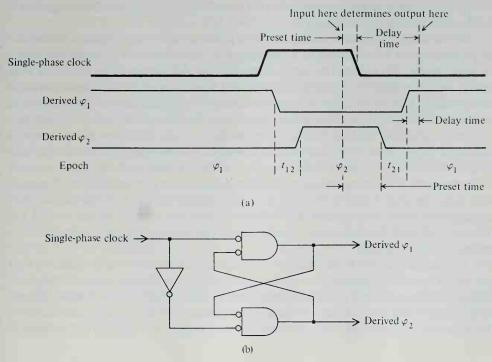

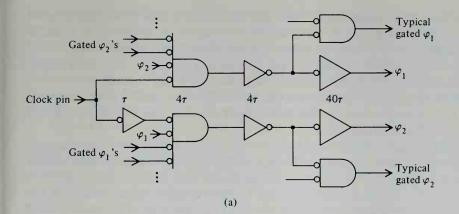

| 3.3 Two-phase clocks                           | 65   |

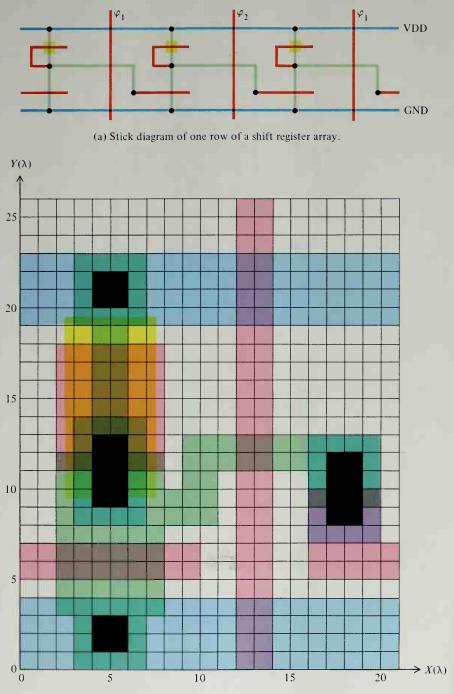

| 3.4 The shift register                         | 66   |

| 3.5 Relating different levels of abstraction   | 68   |

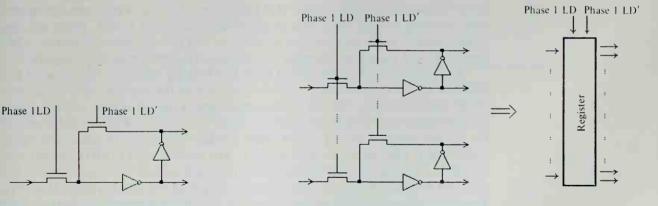

| 3.6 Implementing dynamic registers             | -70  |

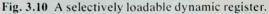

| 3.7 Designing a subsystem                      | 71   |

| 3.8 Register-to-register transfer              | 75   |

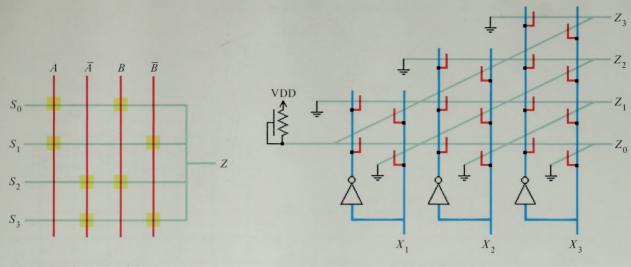

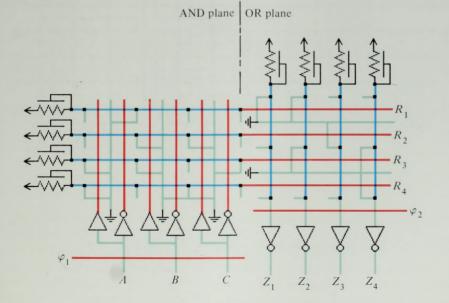

| 3.9 Combinational logic                        | 76   |

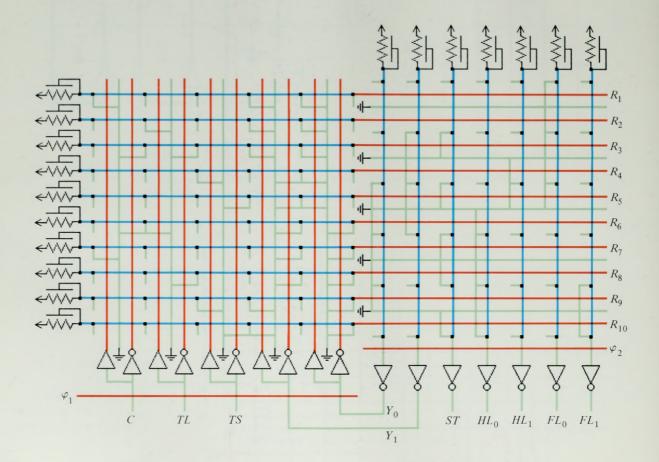

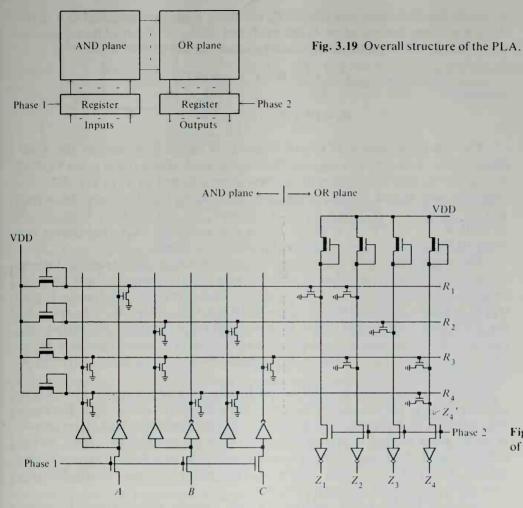

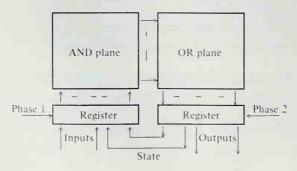

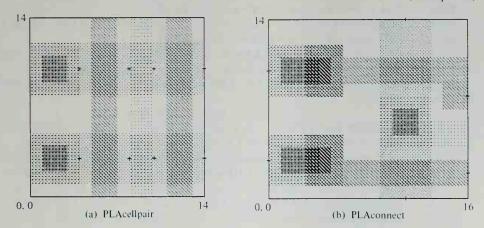

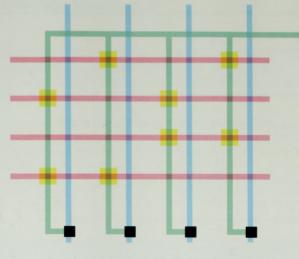

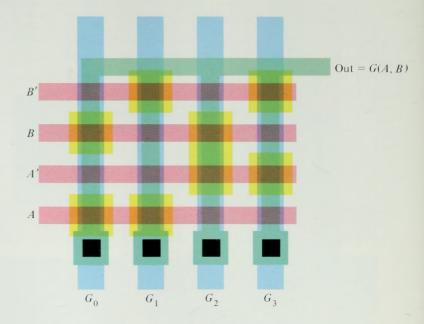

| 3.10 The programmable logic array              | 79   |

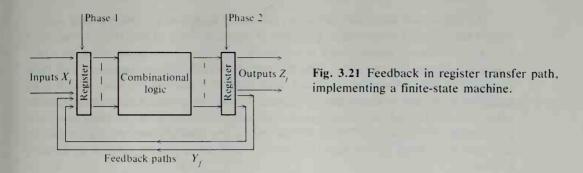

| 3.11 Finite-state machines                     | 82   |

| 3.12 Toward a structured design methodology    | 88   |

| ۲<br>۲ |

|--------|

|--------|

3

### **IMPLEMENTING INTEGRATED SYSTEM DESIGNS: FROM** CIRCUIT TOPOLOGY TO PATTERNING GEOMETRY TO WAFER FABRICATION

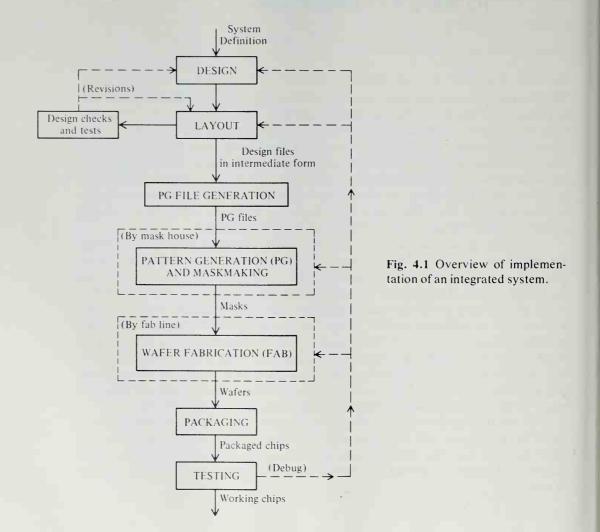

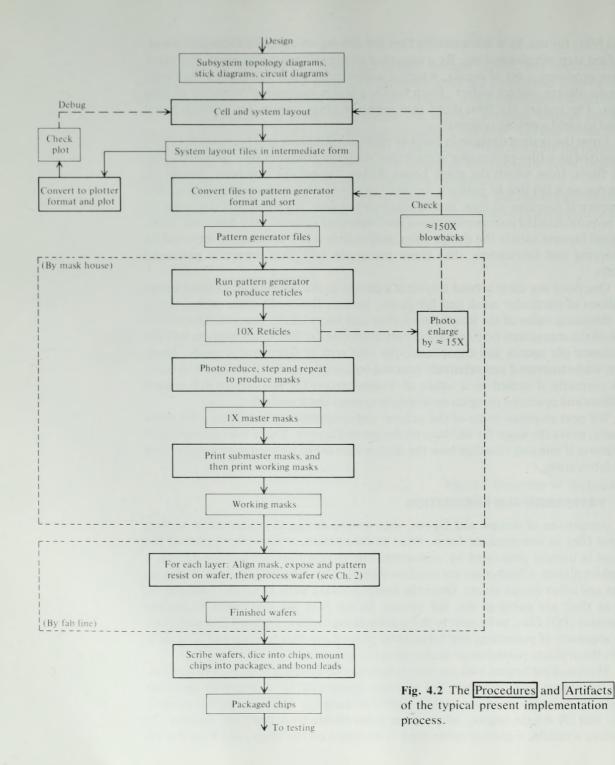

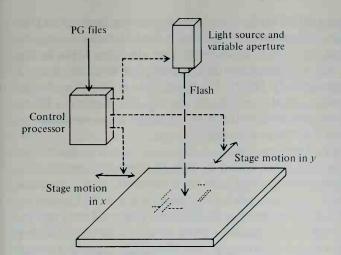

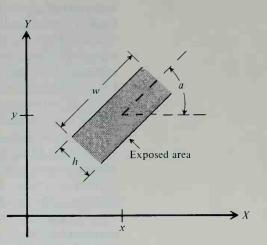

| 4.1 | Introduction                                                  | 92   |

|-----|---------------------------------------------------------------|------|

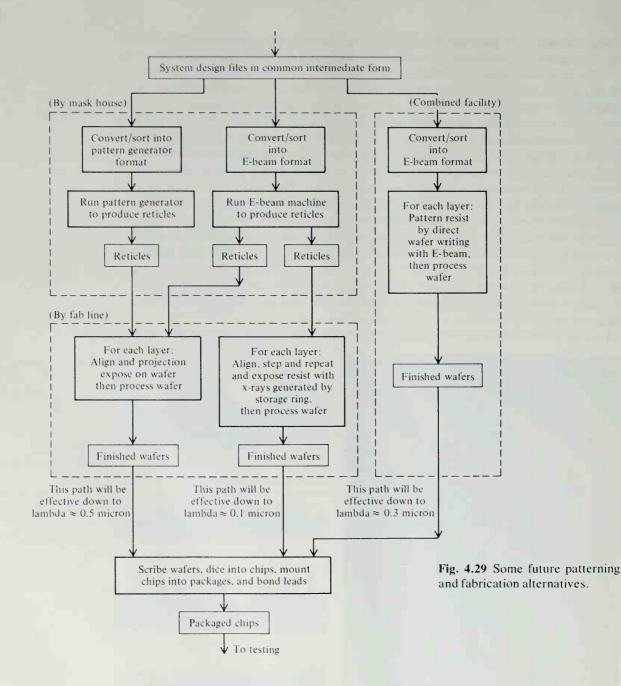

| 4.2 | Patterning and fabrication                                    | 93   |

| 4.3 | Hand layout and digitization using a symbolic layout language | - 98 |

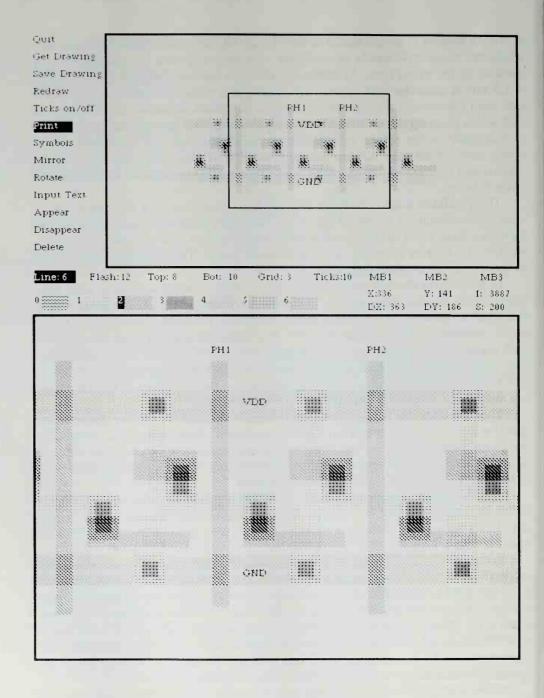

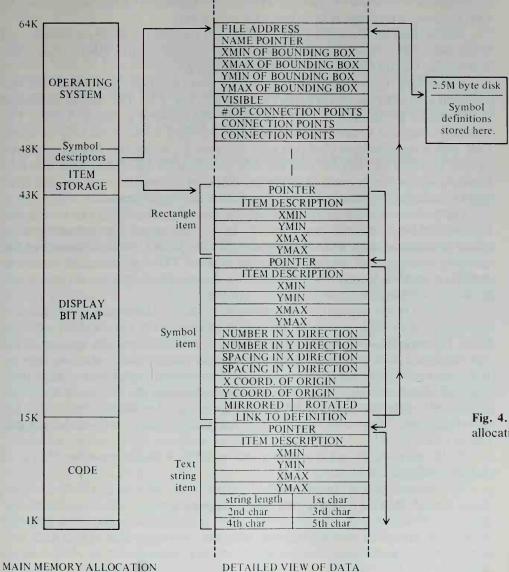

| 4.4 | An interactive layout system                                  | 109  |

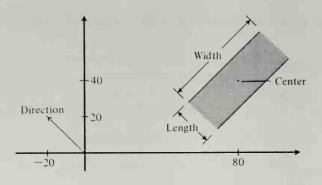

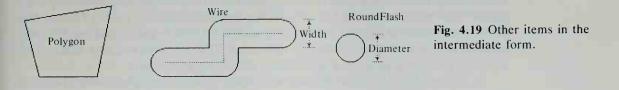

| 4.5 | The Caltech Intermediate Form for LSI layout description      | 115  |

| 4.6 | The multiproject chip                                         | 128  |

| 4.7 | Patterning and fabrication in the future                      | _137 |

91

145

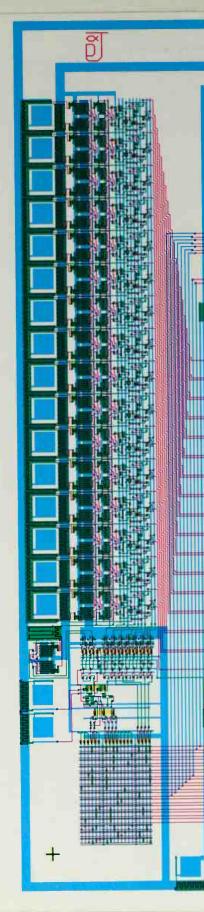

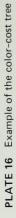

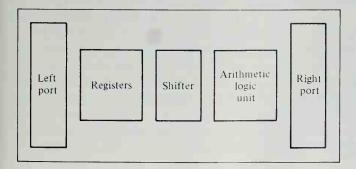

### OVERVIEW OF AN LSI COMPUTER SYSTEM, AND THE DESIGN OF THE OM2 DATA PATH CHIP

| 5.1 | Introduction                           | 145 |

|-----|----------------------------------------|-----|

| 5.2 | The OM project at Caltech              | 146 |

| 5.3 | System overview                        | 147 |

| 5.4 | The overall structure of the data path | 149 |

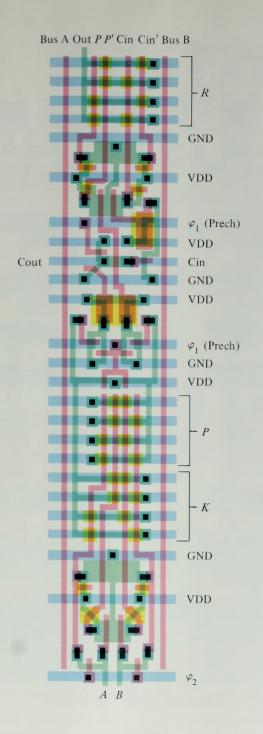

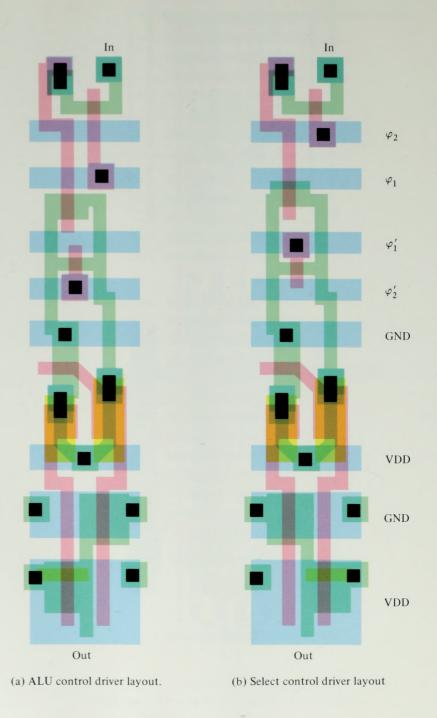

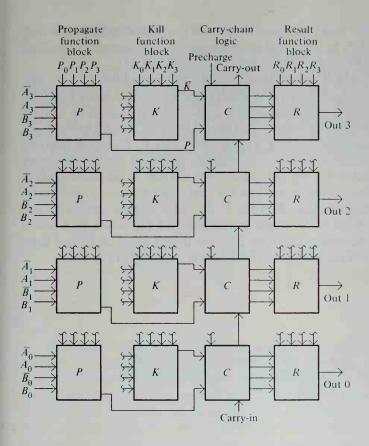

| 5.5 | The arithmetic logic unit              | 150 |

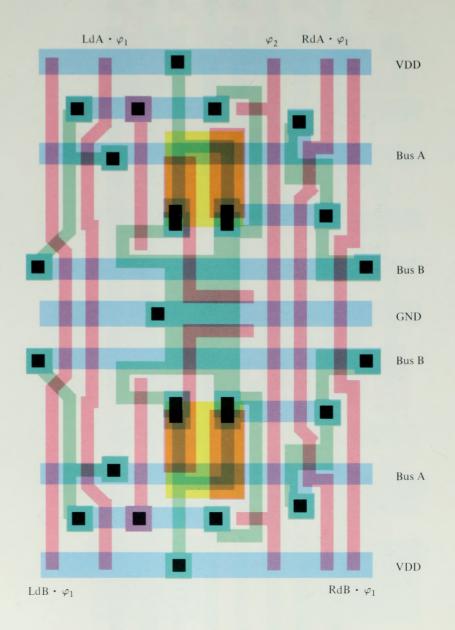

| 5.6 | ALU registers                          | 155 |

| 5.7 | Buses                                  | 156 |

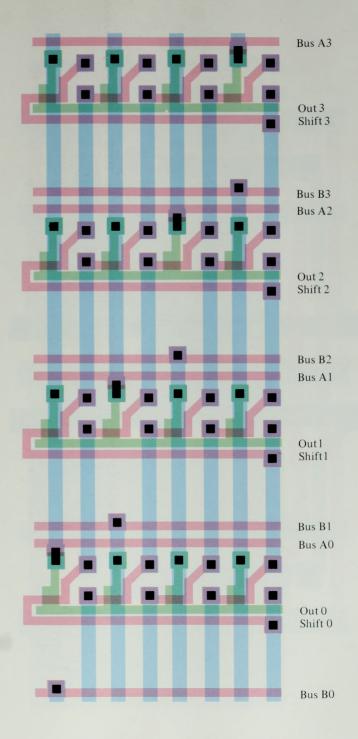

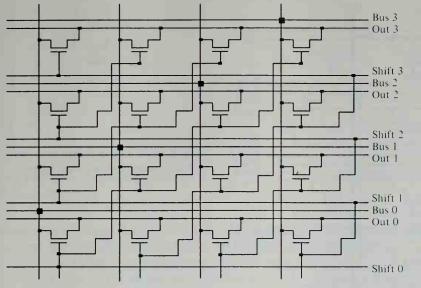

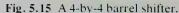

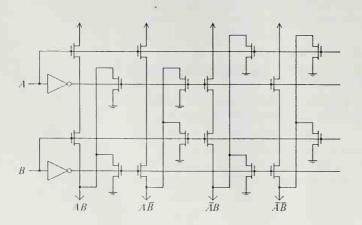

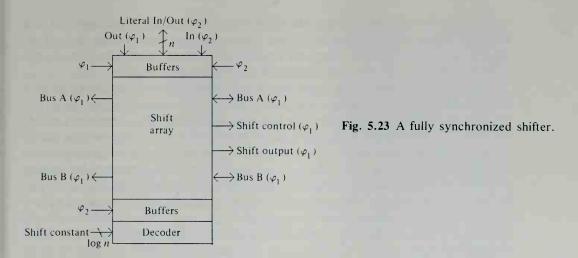

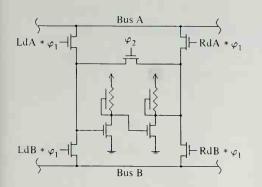

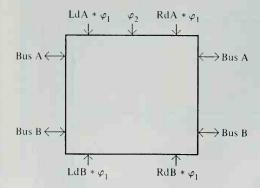

| 5.8 | Barrel shifter                         | 157 |

| 5.9 | Register array                         | 163 |

203

211

216

| 5.10 | Communication with the outside world               | 164 |

|------|----------------------------------------------------|-----|

| 5.11 | Encoding the control operation of the data path    | 166 |

| 5.12 | Functional specification of the OM2 data path chip | 168 |

|      | Appendix                                           | 181 |

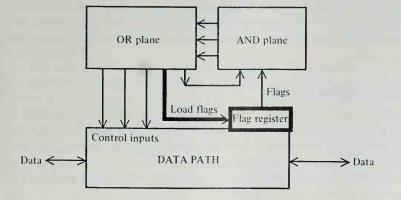

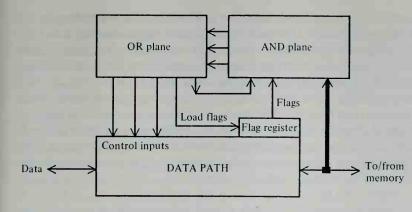

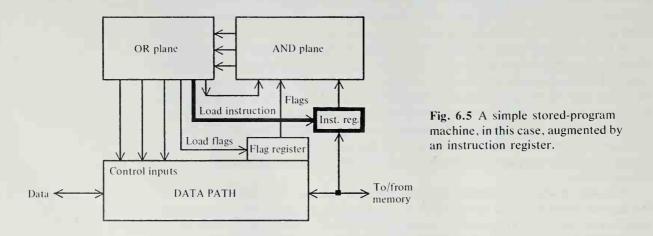

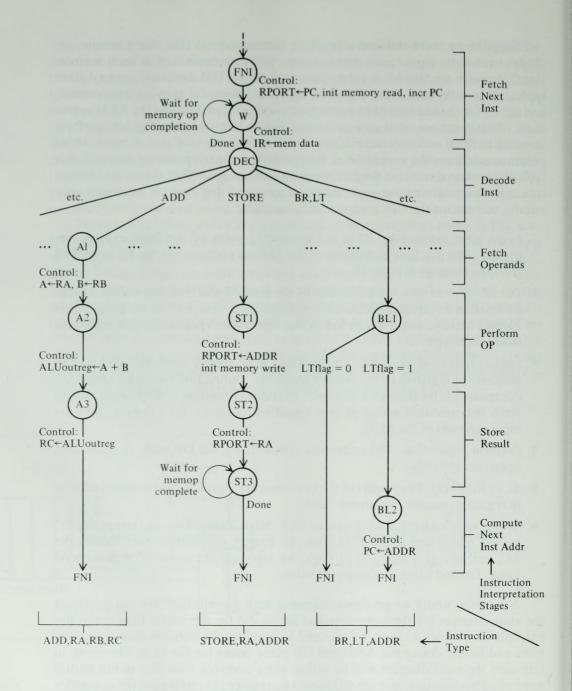

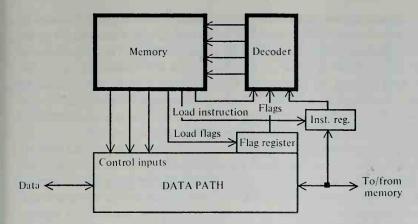

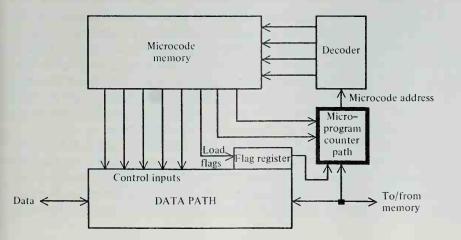

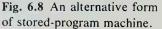

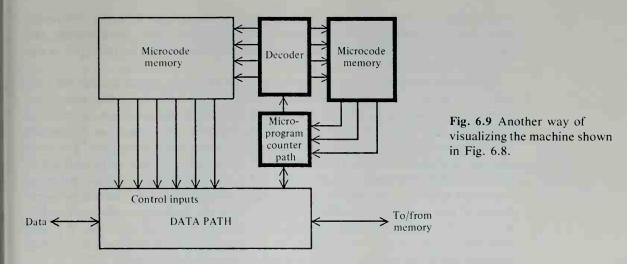

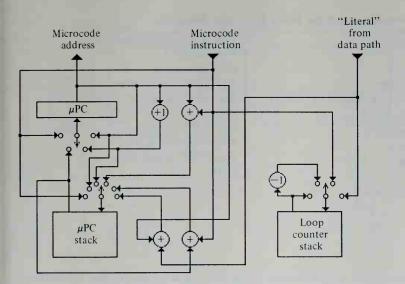

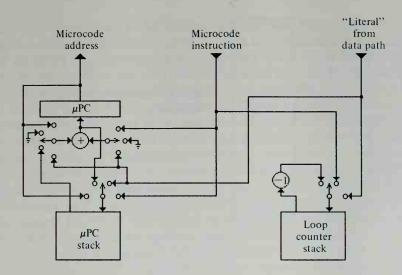

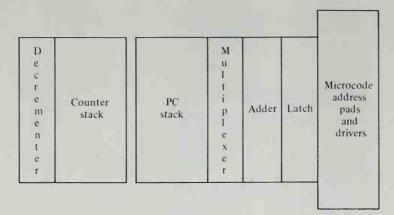

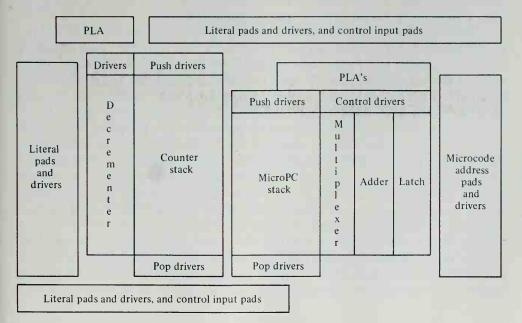

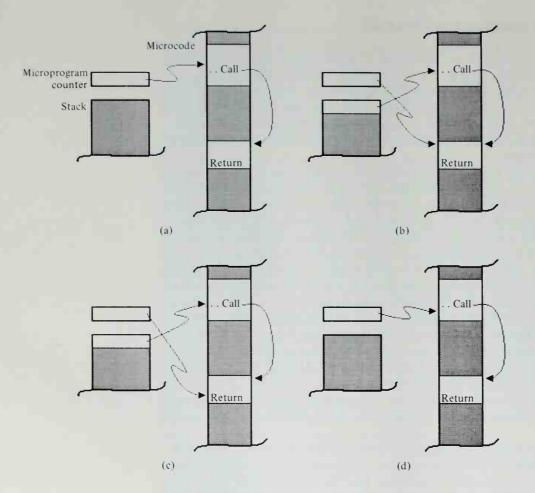

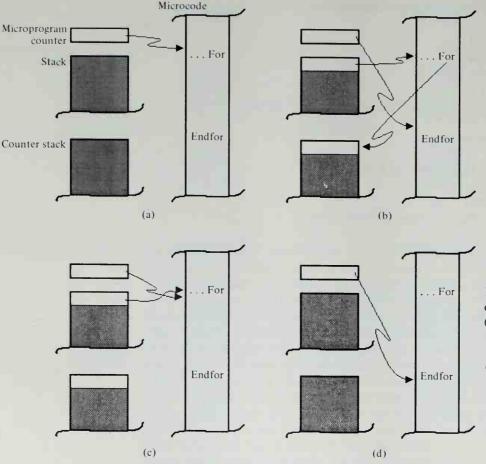

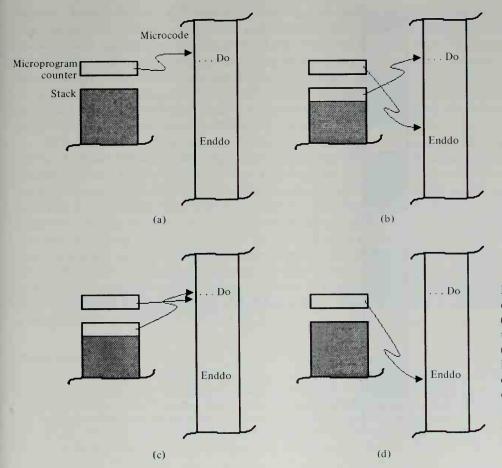

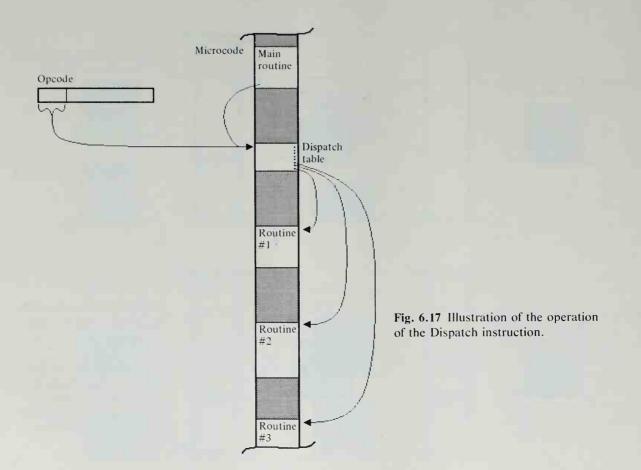

## ARCHITECTURE AND DESIGN OF SYSTEM CONTROLLERS,<br/>AND THE DESIGN OF THE OM2 CONTROLLER CHIP1896.1 Introduction1896.2 Alternative control structures1906.3 The stored-program machine1926.4 Microprogrammed control200

6.6 Examples of controller operation

6.5 Design of the OM2 controller chip

6.7 Some reflections on the classical stored-program machine

| 218 |

|-----|

| 218 |

| 221 |

| 229 |

| 233 |

| 236 |

| 242 |

| 252 |

| 254 |

|     |

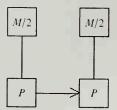

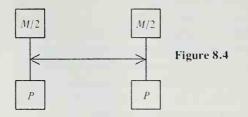

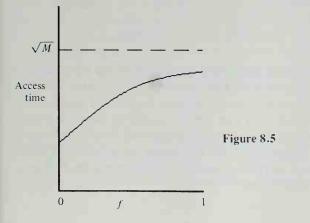

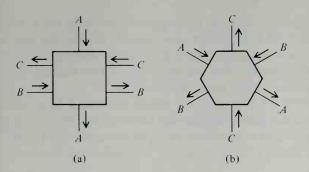

$\bigotimes_{(0)}^{(0)}$ HIGHLY CONCURRENT SYSTEMS 263 263 8.1 Introduction 264 8.2 Communication and concurrency in conventional computers 271 8.3 Algorithms for VLSI processor arrays 292 8.4 Hierarchically organized machines 8.5 Highly concurrent structures with global communication 313 330 8.6 Challenges for the future G

| PHYSICS OF COMPUTATIONAL SYSTEMS              | 333 |

|-----------------------------------------------|-----|

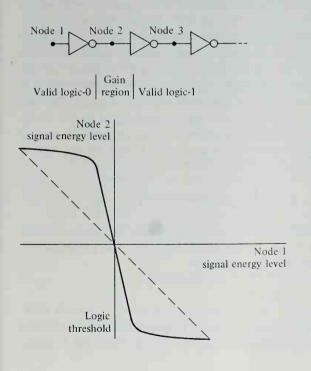

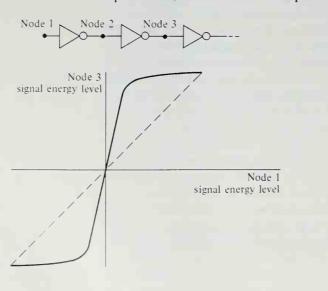

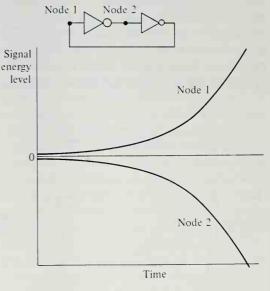

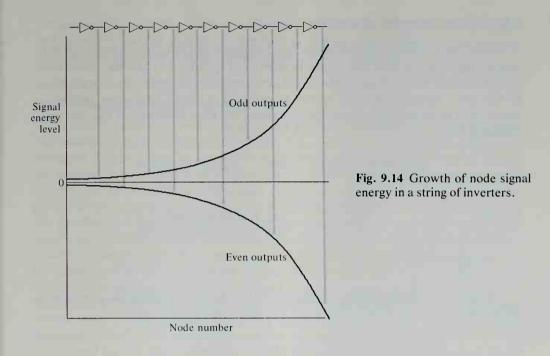

| 9.1 Digital systems                           | 334 |

| 9.2 Voltage limit                             | 341 |

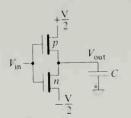

| 9.3 Discreteness of charge                    | 342 |

| 9.4 Transitions in quantum mechanical systems | 343 |

Contents

| 9.5  | Irreversibility                          | 348 |

|------|------------------------------------------|-----|

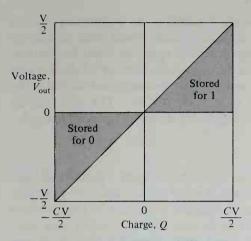

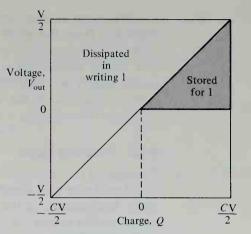

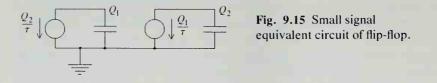

| 9.6  | Memory                                   | 351 |

| 9.7  | Thermal limit                            | 357 |

| 9.8  | Quantum limits                           | 358 |

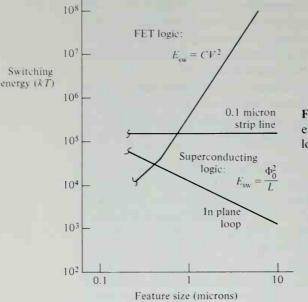

| 9.9  | Two technologies—An example              | 360 |

| 9.10 | Complexity of computation                | 365 |

| 9.11 | Entropic view of computation             | 366 |

| 9.12 | Conclusion                               | 370 |

|      | Further Suggested Reading                | 373 |

|      | Approximate Values of Physical Constants | 379 |

|      | Index                                    | 381 |

xvi

### MOS DEVICES AND CIRCUITS

We begin with a discussion of the basic properties of the *n*-channel, metal-oxidesemiconductor (MOS), field-effect transistor (FET). We then describe and analyze a number of circuits composed of interconnected MOS field-effect transistors. The circuits described are typical of those we will commonly use in the design of integrated systems. The analysis, though highly condensed, is conceptually correct and provides a basis for the solution of most system problems typically encountered.

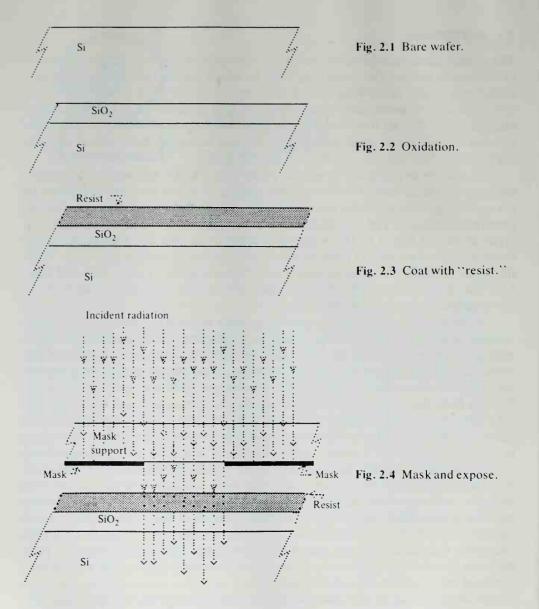

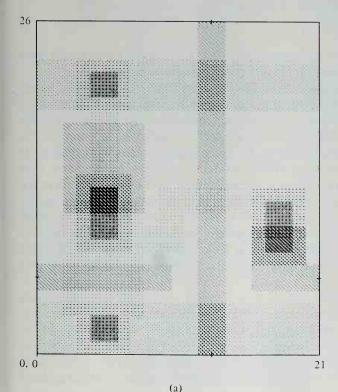

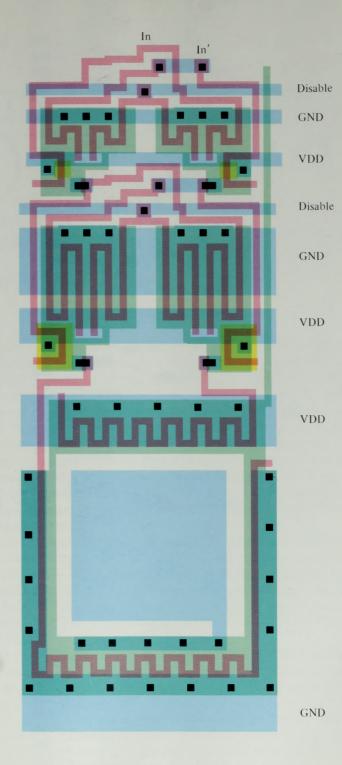

Integrated systems in MOS technology contain three levels of conducting material separated by intervening layers of insulating material. Proceeding from top to bottom, the levels are termed *metal*, *polysilicon*, and *diffusion*, respectively. Patterns for paths on the three levels, and the locations of contact cuts through the insulating material to connect certain points between levels, are transferred into the levels during the fabrication process from *masks* similar to photographic negatives. (Details of the fabrication process will be discussed in Chapter 2.)

In the absence of contact cuts through the insulating material, paths on the metal level may cross over paths on either the polysilicon level or the diffusion level with no significant functional effect. However, wherever a path on the polysilicon level crosses a path on the diffusion level, a transistor is created. Such a transistor has the characteristics of a simple switch, with a voltage on the polysilicon-level path controlling the flow of current in the diffusion-level path. Circuits composed of such transistors, interconnected by patterned paths on the three levels, form our basic building blocks. With these basic circuits, we will design integrated systems, to be fabricated on the surface of monolithic crystalline chips of silicon.

### **1.1 THE MOS TRANSISTOR**

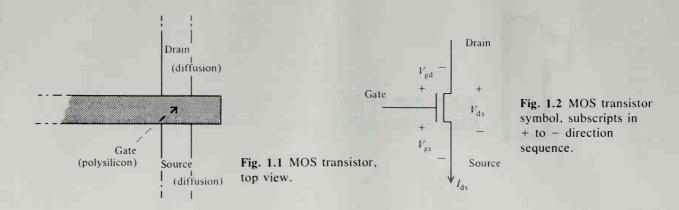

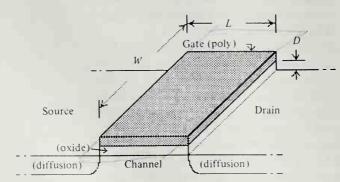

An MOS transistor will be produced on the integrated system chip wherever a polysilicon path crosses a diffusion path, as shown in Fig. 1.1. The electrical sym-

### 2 MOS Devices and Circuits

bol used to represent the MOS transistor in our circuit diagrams is shown in Fig. 1.2, along with symbols and polarities of certain voltages of interest. Note that the source and drain terminals of the device are physically symmetrical. For the *n*-channel MOSFET's the terminal labels are assigned such that drain-to-source voltage  $V_{ds}$  is normally positive. A more detailed view of the rectangular region called the gate, where the polysilicon (poly) crosses the diffusion, is given in Fig. 1.3. During fabrication the diffusion paths are formed after the poly paths are formed (as explained more fully in Chapter 2). The poly gate, and the thin layer of oxide beneath it, mask the region under the gate during diffusion. Therefore, no diffusion path forms under the gate, and there is no direct connection on the diffusion level between the source and drain terminals of the transistor. Metal, poly, and diffusion paths all conduct electricity well enough to be considered "wires" until further notice.

Fig. 1.3 MOSFET gate dimensions.

In the absence of any charge on the gate, the drain-to-source path through the transistor is like an open switch. The gate, separated from the substrate by the layer of thin oxide, forms a capacitor. If sufficient positive charge is placed on the gate so that gate-to-source voltage  $V_{\rm gs}$  exceeds a *threshold voltage*  $V_{\rm th}$ , electrons

will be attracted to the region under the gate to form a conducting path between drain and source. Most of the transistors we will use in our systems have threshold voltages greater than zero. These are called *enhancement mode* MOSFET's and their threshold voltage typically is  $\approx 0.2$  VDD, where VDD is the positive supply voltage for the particular technology.

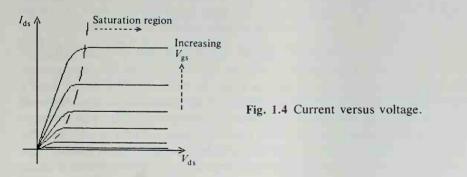

The basic operation performed by the MOS transistor is to use charge on its gate to control the movement of negative charge between source and drain through the channel under the gate. The current from source to drain equals the charge induced in the channel divided by the *transit time* or average time required for an electron to move from source to drain. The transit time itself is the distance the electron has to move divided by its average velocity. In semiconductors under normal conditions, the velocity is proportional to the electric field driving the electrons. The relationship between drain-to-source current  $I_{ds}$ , drain-to-source voltage  $V_{ds}$ , and gate-to-source voltage  $V_{gs}$  is sketched in Fig. 1.4. For small  $V_{ds}$ , the transit time  $\tau$  is given by Eq. 1–1:

$$\tau = \frac{L}{\text{velocity}} = \frac{L}{\mu E} = \frac{L^2}{\mu V_{\text{ds}}} . \tag{1-1}$$

The proportionality constant  $\mu$  is called the *mobility* of the charge carriers, in this case electrons, under the influence of an electric field in the conducting material of the channel region. It is a velocity per unit electric field (cm<sup>2</sup>/volt-sec.). We shall see that the transit time is the fundamental time unit of the entire integrated system.

The amount of negative charge in transit Q is just the gate capacitance times the voltage on the gate in excess of the threshold voltage. The capacitance of two parallel conductors of area A, separated by insulating material of thickness D, equals  $\epsilon A/D$ . The proportionality constant  $\epsilon$  is called the permittivity of the insulating material and has a simple interpretation. It is the capacitance of parallel conductors of area  $A = 1 \text{ cm}^2$ , separated by a thickness D = 1 cm of the insulator material, and is in the units farad/cm. Therefore, the gate capacitance equals

### 4 MOS Devices and Circuits

$\epsilon WL/D$ . Thus the charge in transit is given by Eq. (1-2), and the current is given by Eq. (1-3).

$$Q = -C_{\rm g}(V_{\rm gs} - V_{\rm th}) = -\frac{\epsilon WL}{D} (V_{\rm gs} - V_{\rm th})$$

(1-2)

$$I_{\rm ds} = -I_{\rm sd} = -\frac{\rm charge in transit}{\rm transit time} = \frac{\mu \epsilon W}{LD} (V_{\rm gs} - V_{\rm th})(V_{\rm ds})$$

(1-3)

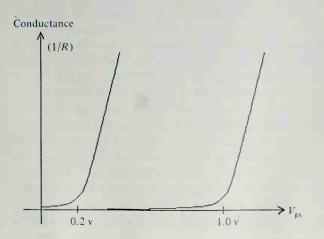

Note that for small  $V_{ds}$ , the drain current is proportional to the source-drain voltage and also to the gate voltage above threshold. Any device with a current through it proportional to the voltage across it may be viewed as a resistor, and in the case of an MOS device with *low* drain-to-source voltage, the resistance is controlled by the gate voltage as given in Eq. (1-4).

$$\frac{V_{\rm ds}}{I_{\rm ds}} = R = \frac{L^2}{\mu C_{\rm g} (V_{\rm gs} - V_{\rm th})}$$

(1-4)

In Eqs. (1-2) and (1-4),  $C_g$  is the gate-to-channel capacitance of the turned-on transistor. In the simple case where this transistor is driving the gate of an identical transistor, the time response of the system will be an exponential with a time constant  $RC_g$ , given in Eq. (1-5). This time constant is similar in form to the expression for transit time  $\tau$  given in Eq. (1-1).

$$RC_{\rm g} = \frac{L^2}{\mu (V_{\rm gs} - V_{\rm th})}$$

(1-5)

Although the above equations are greatly simplified, they provide sufficient information to make many design decisions that we will face, and they also give us insight to the scaling of devices to smaller sizes. In particular, the transit time  $\tau$ can be viewed as the basic time unit of any system we shall build in the integrated technology. In almost all situations, the fastest operation that we can perform is to transfer a signal from the gate of one MOS transistor onto the gate of another. The transit time is the minimum time in which a charge placed on the gate of one transistor results in the transfer of a similar charge through that transistor's channel onto the gate of a subsequent transistor. For example, a transfer of charge from one transistor onto two identical transistors requires a minimum of two transit times. Thus, the transit time of the basic transistor in an integrated system can be viewed as the unit of time in which all other times in the system are scaled. Although it is a somewhat optimistic approximation, we will use  $\tau$  as the primary time metric in calculating the delay through elementary inverting-logic stages. More accurate predictions of circuit behavior can be produced using any one of a number of available circuit simulation programs.<sup>1,2</sup>

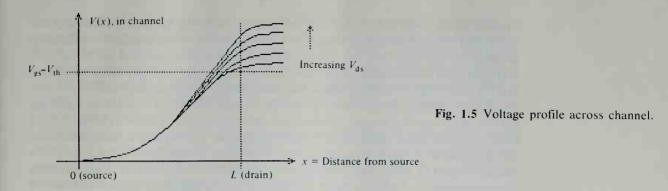

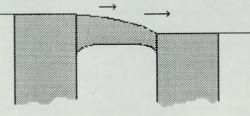

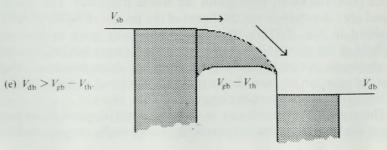

As  $V_{\rm ds}$  is increased, not all the drain-to-source voltage is available for reducing the transit time. Drain voltage in excess of one threshold below the gate voltage creates a short region of high electric field, adjacent to the drain, that the carriers cross very quickly. The electric field in the major portion of the channel from the source up to this region is proportional to  $V_{\rm gs} - V_{\rm th}$ , as shown in Fig. 1.5. For  $V_{\rm ds} > (V_{\rm gs} - V_{\rm th})$ , the drain current becomes independent of  $V_{\rm ds}$ . Further increases in  $V_{\rm ds}$  neither increase  $I_{\rm ds}$  nor decrease the transit time. This range of  $V_{\rm ds}$  values is known as *saturation*. In saturation,

$$I_{\rm ds} = \frac{\mu \epsilon W}{2LD} (V_{\rm gs} - V_{\rm th})^2. \tag{1-6}$$

With the exception of the factor of 2 in the denominator, Eq. (1-6) is similar to Eq. (1-3), with the  $V_{\rm ds}$  factor in (1-3) replaced by its maximum effective value,  $V_{\rm gs} - V_{\rm th}$ . The factor of 2 in Eq. (1-6) arises from the nonuniformity of the electric field in the channel region when in saturation.<sup>3</sup> (Richman, 1973)

### **1.2 THE BASIC INVERTER**

The first logic circuit we will describe is the basic digital inverter. Analysis of this circuit is then extended to analysis of basic NAND and NOR logic gates. The inverter's logic function is to produce an output that is the complement of its input. When describing the logic function of circuits in integrated systems, we assign the value logic-1 to voltages equaling or exceeding some defined logic threshold voltage, and logic-0 to voltages less than this threshold voltage.

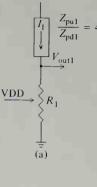

Were there an efficient way to implement resistors in the MOS technology, we could build a basic digital inverter circuit using the configuration of Fig. 1.6. Here, if the inverter input voltage  $V_{in}$  is less than the transistor threshold voltage  $V_{th}$ , then the transistor is switched off and  $V_{out}$  is "pulled up" to the positive supply voltage VDD. In this case the output is the complement of the input. If  $V_{in}$  is greater than  $V_{th}$ , the transistor is switched on and current flows from the VDD supply through the resistor R to GND. If R were sufficiently large,  $V_{out}$  could be

Fig. 1.6 An inverter.

"pulled down" well below  $V_{th}$ , thus again complementing the input. However, the resistance per unit length of minimum-width lines of various available conducting elements is far less than the effective resistance of the switched on MOSFET. Implementing a sufficiently large inverter pull-up using resistive lines would require a very large area compared to that occupied by the transistor itself.

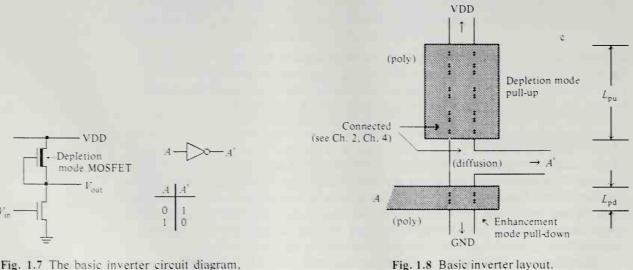

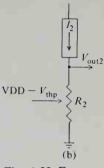

To circumvent this problem a *depletion mode* MOSFET is used as a pull-up for the basic inverter circuit, symbolized and configured as shown in Fig. 1.7. In contrast to the usual enhancement mode transistor, the depletion mode transistor has a threshold voltage,  $V_{dep}$ , that is less than zero. During fabrication, one of the masks is used to select any desired subset of transistors in the integrated system for processing as depletion mode transistors. For a depletion mode transistor to turn off, a voltage is required on its gate relative to its source that is more negative than  $V_{dep}$ . But the depletion mode pull-up transistor's gate is connected to its source, and thus it is always turned on. Hence, when the enhancement mode transistor is turned off (for example, by connecting zero voltage to its gate) the output of the inverter will be equal to VDD. We will find that for reasonable ratios of the gate geometries of the two transistors, input voltages above a defined logic threshold voltage,  $V_{inv}$ , will produce output voltages below that logic threshold voltage, and vice versa.

Fig. 1.7 The basic inverter circuit diagram, logic symbol, and logic function.

The top view of the layout of an inverter on the silicon surface is sketched in Fig. 1.8. It consists of two polysilicon regions overhanging a path in the diffusion level that runs between VDD and GND. This arrangement forms the two MOS transistors of the inverter. The inverter input A is connected to the poly that forms

Fig. 1.

the gate of the lower of the two transistors. The pull-up is formed by connecting the gate of the upper transistor to its source. (The layout geometry and fabrication details of such connections are described in Chapter 2.) The output of the inverter is shown emerging on the diffusion level, from between the drain of the pull-down and the source of the pull-up. The pull-up is a depletion mode transistor, and it is usually several times longer than the pull-down in order to achieve the proper inverter logic threshold.

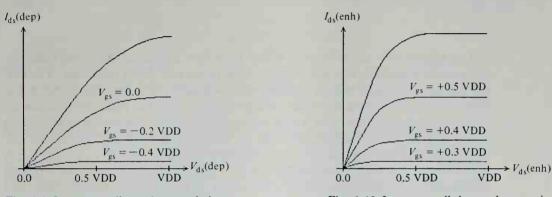

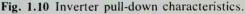

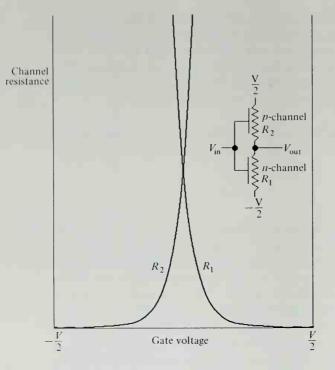

Figures 1.9 and 1.10 show the characteristics of a typical pair of MOS transistors used to implement an inverter. The relative locations of the saturation regions of the pull-up and pull-down differ in these characteristics, due to the difference in the threshold voltages of the transistors.

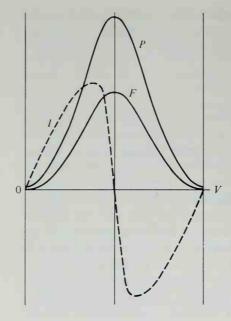

Fig. 1.9 Inverter pull-up characteristics.

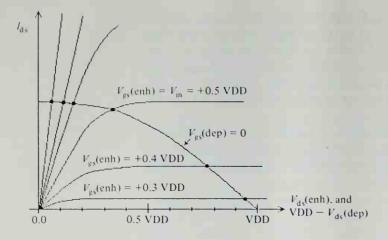

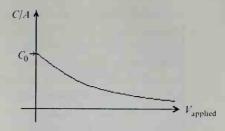

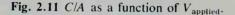

We can use a graphical construct to determine the actual transfer characteristic,  $V_{out}$  versus  $V_{in}$ , of the inverter circuit. From Fig. 1.7 we see that  $V_{ds}(enh)$  of the enhancement mode transistor equals VDD minus  $V_{ds}(dep)$  of the depletion mode transistor. Also,  $V_{ds}(enh)$  equals  $V_{out}$ . In a steady state and with no current drawn from the output, the  $I_{ds}$  of the two transistors is equal. Since the pull-up has its gate connected to its source, only one of its characteristic curves is relevant, namely the one for  $V_{gs}(dep) = 0$ . Taking these facts into account, we begin the graphical solution (Fig. 1.11) by superimposing plots of  $I_{ds}(enh)$  versus  $V_{ds}(enh)$ and the one plot of  $I_{ds}(dep)$  versus [VDD –  $V_{ds}(dep)$ ]. Since the currents in both transistors must be equal, the intersections of these sets of curves yield  $V_{ds}(enh)$ =  $V_{out}$ , versus  $V_{gs}(enh) = V_{in}$ . The resulting transfer characteristic is plotted in Fig. 1.12.

While studying Figs. 1.11 and 1.12, consider the effect of starting with  $V_{in} = 0$  and then gradually increasing  $V_{in}$  towards VDD. While the input voltage is below the threshold of the pull-down transistor, no current flows in that transistor, the output voltage is constant at VDD, and the drain-to-source voltage across the

Fig. 1.11  $I_{ds}(enh)$  versus  $V_{ds}(enh)$ , and  $I_{ds}(dep)$  versus [VDD -  $V_{ds}(dep)$ ].

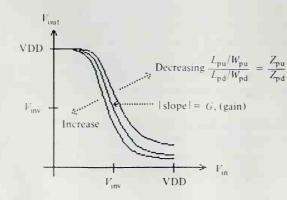

pull-up transistor is equal to zero. When  $V_{in}$  is first increased above the enhancement mode threshold, current begins to flow in the pull-down transistor. The output voltage decreases slowly as the input voltage is first increased above  $V_{\rm th}$ . Subsequent increases in the input voltage rapidly lower the pull-down's drain-tosource voltage, until the point is reached where the pull-down leaves its saturation region and becomes resistive. Then as  $V_{in}$  continues to increase, the output voltage asymptotically approaches zero. The input voltage at which  $V_{in}$  equals  $V_{out}$  is known as the logic threshold voltage  $V_{inv}$ . Figure 1.12 also shows the effect of changes in the transistor length-to-width ratios on the transfer characteristics and on the logic threshold voltage. The resistive impedance of the MOS transistor is proportional to the *length-to-width ratio* Z of its gate region. Using the subscripts pu (for the pull-up transistor) and pd (for the pull-down transistor) we find that if  $Z_{\rm pu} = L_{\rm pu}/W_{\rm pu}$  is increased relative to  $Z_{\rm pd} = L_{\rm pd}/W_{\rm pd}$ , then  $V_{\rm inv}$  decreases, and vice versa. The gain G, or negative slope of the transfer characteristic near  $V_{inv}$ , increases as  $Z_{pu}/Z_{pd}$  increases. The gain must be substantially greater than unity for digital circuits to function properly.

Fig. 1.12  $V_{out}$  versus  $V_{in}$  for the basic inverter.

### 1.2.1 Inverter Logic Threshold Voltage

The most fundamental property of the basic inverter circuit is its logic threshold voltage,  $V_{inv}$ . The logic threshold here is not the same as  $V_{th}$  of the enhancement mode transistor; it is that voltage on the input of the enhancement mode transistor that causes an equal output voltage. If  $V_{in}$  is increased above this logic threshold,  $V_{out}$  falls below it, and if  $V_{in}$  is decreased below  $V_{inv}$ ,  $V_{out}$  rises above it. The following simple analysis assumes that both pull-up and pull-down are in saturation, so that Eq. (1-6) applies. Usually the pull-up is not quite in saturation, but the following is still nearly correct:  $V_{inv}$  is approximately that input voltage that would cause saturation current through the pull-down transistor to be equal to saturation for equality of the two currents given in Eq. (1-6), we find the condition for equality of the two currents given in Eq. (1-7). Currents are equal when

$$\frac{W_{\rm pd}}{L_{\rm pd}} (V_{\rm inv} - V_{\rm th})^2 = \frac{W_{\rm pu}}{L_{\rm pu}} (-V_{\rm dep})^2; \qquad (1-7)$$

thus,

$$V_{\rm inv} = V_{\rm th} - \frac{V_{\rm dep}}{\sqrt{Z_{\rm pu}/Z_{\rm pd}}} . \qquad (1-7a)$$

Here we note that the current through the depletion mode transistor is dependent only on its geometry and threshold voltage  $V_{dep}$ , since its  $V_{gs} = 0$ . Note that  $V_{inv}$  is dependent on the thresholds of both the enhancement and depletion mode transistors and also on the square root of the ratio of the Z = L/W of the enhancement mode transistor to Z = L/W of the depletion mode transistor.

Various possible choices of values for these threshold voltages can be traded off against the areas and current driving capability of transistors in the system's inverters. To maximize  $(V_{\rm gs} - V_{\rm th})$  and increase the pull-downs' current driving capability for a given area,  $V_{\rm th}$  should be as low as possible. However, if  $V_{\rm th}$  is too low, inverter outputs won't be driveable below  $V_{\rm th}$ , and inverters won't be able to turn off transistors used as simple switches. The original choice of  $V_{\rm th} \approx 0.2$  VDD is a reasonable compromise here.

Similarly, to maximize the current driving capability of pull-ups of given area, we might set the system's  $V_{dep}$  as far negative as possible. However, Eq. (1-7a) shows that for chosen  $V_{inv}$  and  $V_{th}$ , decreasing  $V_{dep}$  requires an increase in  $L_{pu}/W_{pu}$ , typically leading to an increase in pull-up area. The compromise made in this case is often as follows. The negative threshold of depletion mode transistors is set during fabrication such that with gate tied to source, they turn on approximately as strongly as would an enhancement mode transistor with VDD connected to its gate and its source grounded. In other words, depletion mode transistors and enhancement mode transistors of equal gate dimensions would have equal drain-to-source currents under those conditions. Applying Eq. (1-7) in those conditions, we find that

$$(-V_{\rm dep})^2 \approx (VDD - V_{\rm th})^2$$

### 10 MOS Devices and Circuits

Therefore,  $-V_{dep} \approx (VDD - V_{th})$ , and  $V_{dep} \approx -0.8$  VDD. Adjustments in the details of the choice of  $V_{dep}$  are often made in the interest of optimization of processes for particular products. Perhaps the most common choice is that of  $V_{dep} \sim -0.6$  VDD (leading to smaller pull-up areas than would  $V_{dep} \sim -0.8$  VDD). Substituting this choice of  $V_{dep}$  into Eq. (1-7a), we find that

$$V_{\rm inv} \approx 0.2 \text{ VDD} + \frac{0.6 \text{ VDD}}{\sqrt{Z_{\rm pu}/Z_{\rm pd}}}.$$

(1-8)

In general it is desirable that the margins around the inverter threshold be approximately equal, i.e., that the inverter threshold,  $V_{inv}$ , lie approximately midway between VDD and ground. We see from Eq. (1-8) that this criterion is met by a ratio of pull-up Z to pull-down Z of approximately 4:1.

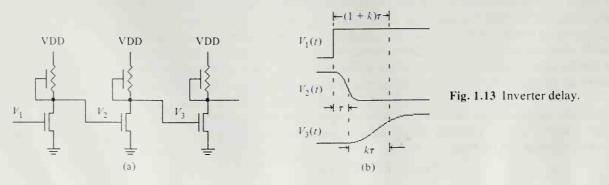

### **1.3 INVERTER DELAY**

A minimum requirement for an inverter is that it drive another identical to itself. Let us analyze the delay through a string of inverters of identical dimensions. This is the simplest case in which we can estimate performance. Inverters connected in this way are shown in Fig. 1.13(a). We define the *inverter ratio* k as the ratio of Z of the pull-ups to Z of the pull-downs. We will sometimes use the alternative "resistor-with-gate" pull-up symbol, as in Fig. 1.13(a), to clarify its functional purpose.

Let us assume that prior to t = 0, the voltage at the input of the first inverter is zero, hence the voltage output of the second inverter will be low. At time t = 0, let us place a voltage equal to VDD on the input of the first inverter and visualize the sequence of events that follows. The output of the first inverter, which leads to the gate of the second inverter, will initially be at VDD. Within approximately one transit time, the pull-down transistor of the first inverter will remove from this node an amount of charge equal to VDD times the gate capacitance of the pulldown of the second inverter. The pull-up transistor of the second inverter is now faced with the task of supplying a similar charge to the gate of the third inverter, to

raise it to VDD. Since it can supply at most only 1/k of the current that can be supplied by the pull-down transistor, the delay in the second inverter stage is approximately k times that of the first.

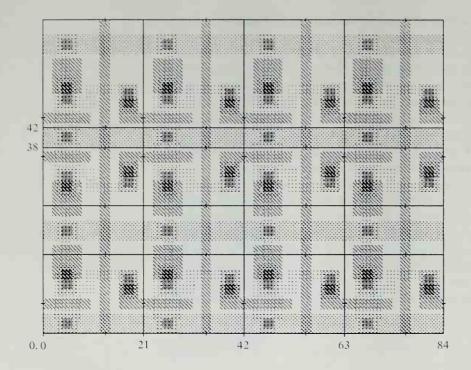

It is thus convenient to speak of the *inverter pair delay* that includes the delay for one "low-going" transition and one "high-going" transition. Inverter pair delay is approximately (1 + k) times the transit time, as shown in Fig. 1.13(b). The fact that the rising transition is slower than the falling transition, by approximately the geometry ratios of the inverter transistors, is an inherent characteristic of any ratio-type logic. It is not true of all logic families. For example, in families such as complementary MOS (CMOS), where there are both *p* MOS and *n* MOS devices on the same silicon chip and both types operate strictly as pull-down enhancement mode devices, any delay asymmetry is a function of the difference in mobilities of the *p*- and *n*-type charge carriers rather than of the transistor geometrical ratios.

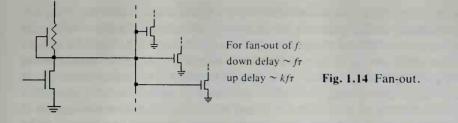

Figure 1.14 shows an inverter driving the inputs of several other inverters. In this case, for a "fan-out" factor f, it is clear that in either the pull-up or pull-down direction, the active device must supply f times as much charge as it did in the case of driving a single input. In this case, the delay in both the "up-going" and "down-going" directions is increased by approximately the factor f. In the case of the down-going transition, the delay is approximately f times the transit time of the pull-down transistor, and in the case of the up-going transition, the delay is approximately the factor times the pull-down transit time.

In the discussions of transit time given earlier, it was assumed that both the depletion mode pull-up device and the enhancement mode pull-down device were operating in the resistive region. It was also assumed that all capacitances were constant, and not a function of voltage. These conditions are not strictly met in the technology we are discussing. Delay calculations given in this text are based on a "switching model" where individual stages spend a small fraction of their time in the midrange of voltages around  $V_{inv}$ . This assumption introduces a small error of the order of 1/G. Because of these and other second-order effects, the switching times actually observed vary somewhat from those derived.

### 1.4 PARASITIC EFFECTS

In integrated systems, capacitances of circuit nodes are due not only to the capacitance of gates connected to the nodes but also to capacitances to ground of signal paths connected to the nodes and to other stray capacitances. These stray capacitances, sometimes called parasitic capacitances, are not negligible. While gate capacitances are typically an order of magnitude greater per unit area than capacitances of the signal paths, the signal paths are often much larger in area than the associated gate regions. Therefore, a substantial fraction of the delay encountered may be accounted for by stray capacitance rather than by the inherent properties of the active transistors. In the simplest case where the capacitance of a node is increased by the presence of parasitic area attached to the node, the delays can be accounted for by simply increasing the transit time by the ratio of the total capacitance to that of the gate of the transistor being driven. Time is required to supply charge not only to the gate itself but also to the parasitic capacitance.

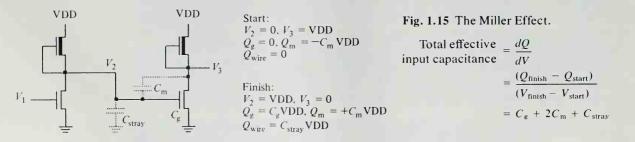

There is one type of parasitic capacitance, however, which is not accounted for so simply. All MOS transistors have a parasitic capacitance between the drain edge of the gate and the drain node. This effect is shown schematically in Fig. 1.15. In an inverter string, this capacitance will be charged in one direction for one polarity of input and in the opposite direction for the opposite polarity input. Thus, on a gross scale its effect on the system is twice that of an equivalent parasitic capacitance to ground. Therefore, gate-to-drain capacitances should be approximately doubled, and added to the gate capacitance  $C_g$  and the stray capacitances, to account for the total capacitance of the node and thus for the effective delay time of the inverter. The effective inverter pair delay then is equal to  $\tau(1 + k) C_{total}/C_g$ .

### 1.5 DRIVING LARGE CAPACITIVE LOADS

As we have seen, the delay per inverter stage is multiplied by a fan-out factor. The overall performance of a system may be seriously degraded if it contains any large fan-outs, where one circuit within the system is required to drive a large capacitive load. As we shall see, this situation often occurs in the case of control drivers required to drive a large number of inputs to memory cells or logic function blocks. A similar and more serious problem is driving wires that go off the silicon chip to other chips or input/output devices. In such cases the ratio of the capacitance that must be driven to the inherent capacitance of a gate circuit on the chip is often many orders of magnitude, causing a serious delay and a degradation of system performance.

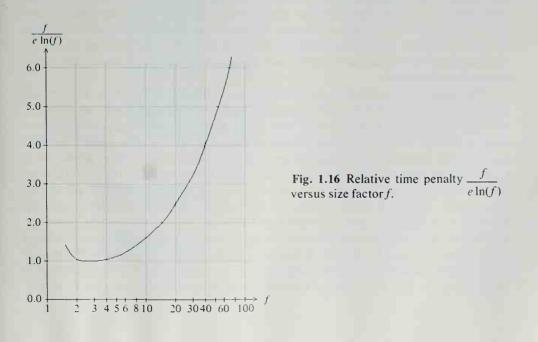

Consider how we may drive a capacitive load  $C_{\rm L}$  in the minimum possible time given that we are starting with a signal on the gate of an MOS transistor of capacitance  $C_{g}$ .<sup>4</sup> Define the ratio of the load capacitance to the gate capacitance,  $C_{L}/C_{g}$ , as Y. It seems intuitively clear that the optimum way to drive a large capacitance is to use our elementary inverter to drive a larger inverter and that larger inverter to drive a still larger inverter until at some point the larger inverter is able to drive the load capacitance directly. Using an argument similar to the fan-out argument, it is clear that for one inverter to drive another inverter, where the second is larger in size by a factor of f, results in a delay f times the inherent inverter delay,  $\tau$ . If N such stages are used, each larger than the previous by a factor f, then the total delay of the inverter chain is  $Nf\tau$ , where  $f^N$  equals Y. Note that if we use a large factor f, we can get by with few stages, but each stage will have a long delay. If we use a smaller factor f, we can shorten the delay of each stage, but we are required to use more stages. What value of N minimizes the overall delay for a given Y? We compute this value as follows: Since  $f^N = Y$ ,  $\ln(Y) = N \ln(f)$ , and the delay of one stage equals  $f_{\tau}$ ; thus the total delay is

$$Nf\tau = \ln(Y)[f/\ln(f)]\tau.$$

(1-9)

Notice that the delay is always proportional to  $\ln(Y)$ , a result of the exponential growth in successive stages of the driver. The multiplicative factor,  $f/\ln(f)$ , is plotted as a function of f in Fig. 1.16, normalized to its minimum value (e). Total delay is minimized when each stage is larger than the previous one by a factor of e, the

base of natural logarithms. Minimum total delay,  $t_{\min}$ , is the elementary inverter delay  $\tau$  times *e* times the natural logarithm of the ratio of the load capacitance to the elementary inverter capacitance:

$$t_{\min} \approx \tau e \ln\left(\frac{C_{\rm L}}{C_{\rm g}}\right).$$

(1-10)

Minimum delay through the driver is seldom the only design criterion. The relative time penalty introduced by the choice of other values of f can be read directly from Fig. 1.16.

### 1.6 SPACE VERSUS TIME

From the results of the sections on inverter delay, parasitic effects, and driving large capacitances, we see that areas and distances on the silicon surface trade off against delay times. For an inverter to drive another inverter some distance away, it must charge not only the gate capacitance of the succeeding inverter but also the capacitance to ground of the signal path connecting the two. Increasing the distance between the two inverters will therefore increase the inverter pair delay. This effect can be counterbalanced by increasing the area of the first inverter, so as to reduce the ratio of the load capacitance to the gate capacitance of the first inverter. But the delay of some previous driving stage is then increased. There is no way to get around the fact that transporting a signal from one node to another some distance away requires either charging or discharging capacitance and therefore takes time. Note that this is not a velocity of light limitation, as is often the case outside the chip. The times are typically several orders of magnitude longer than those required for light to traverse the distances involved. To minimize both the time and space required to implement system functions, we will tend to use the smallest possible circuits and locate them in ways that tend to minimize the interconnection distances.

The results of a previous section can be used here to illustrate another interesting space-versus-time effect. Suppose that the minimum-sized transistors of an integrated system have a transit time  $\tau$  and gate capacitance  $C_g$ . A minimumsized transistor within the system produces a signal that is then passed through successively larger inverting logic stages and eventually drives a large capacitance  $C_L$  with minimum total delay equal to  $t_{\min}$ . With the passage of time, fabrication technology improves. We replace the system with another in which all circuit dimensions, including those vertical to the surface, are scaled down in size by dividing by a factor  $\alpha$ , and the values of VDD and  $V_{\text{th}}$  are also scaled down by dividing by  $\alpha$ . The motivation for this scaling is clear: the new system may contain  $\alpha^2$  as many circuits. As described in a later section, we will find that the transit times of the smallest circuits will now be  $\tau' = \tau/\alpha$ , and their gate capacitance will be  $C'_g = C_g/\alpha$ . The new ratio of load to minimum gate capacitance is  $Y' = \alpha Y$ . Referring to Eq. (1-10), we find the new minimum total delay,  $t'_{min}$ , to drive  $C_L$  scales as follows:

$$t'_{\min} = t_{\min} \left(\frac{1}{\alpha}\right) \left(1 + \frac{\ln \alpha}{\ln Y}\right).$$

Therefore, as the inverters scale down and  $\tau$  gets smaller, more inverting logic stages are required to obtain the minimum "off-chip" delay. Thus the relative delay to the outside world becomes larger. However, the absolute delay becomes smaller.

### 1.7 BASIC NAND AND NOR LOGIC CIRCUITS

NAND and NOR logic circuits may be constructed in integrated systems as simple expansions of the basic inverter circuit. The analysis of the behavior of these circuits, including their logic threshold voltages, transistor geometry ratios and time delays, is also a direct extension of the analysis of the basic inverter.

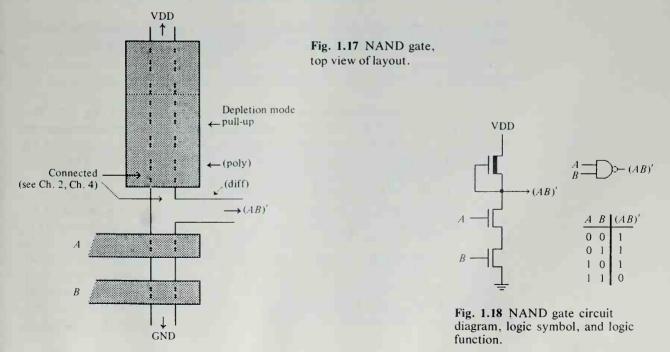

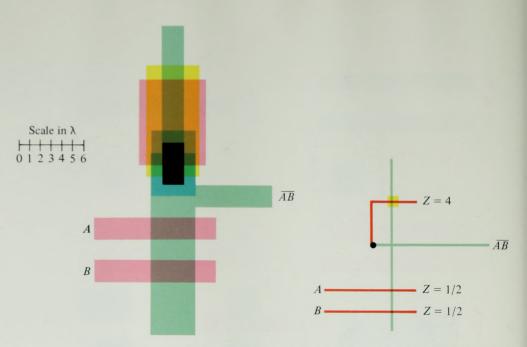

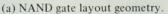

The circuit layout diagram of a two-input NAND gate is shown in Fig. 1.17. The layout is that of a basic inverter with an additional enhancement mode transistor in series with the pull-down transistor. NAND gates with more inputs may be constructed by simply adding more transistors in series with the pull-down path. The electrical circuit diagram, truth table, and logic symbol for the two-input NAND gate are shown in Fig. 1.18. If either of the inputs A or B is a logic-0, the

pull-down path is open and the output will be high and therefore a logic-1. For the output to be driven low, to logic-0, both inputs must be high, at logic-1. The logic threshold voltage of this NAND gate is calculated in a manner similar to that of the basic inverter, except that Eq. (1-8) is rewritten with the length of the pull-downs replaced with the sum of the lengths of the two pull-downs (assuming their widths are equal) as follows:

$$V_{\rm thNAND} \approx rac{

m VDD}{\sqrt{rac{L_{

m pu}/W_{

m pu}}{(L_{

m pd}_{

m a}+L_{

m pd}_{

m b})/W_{

m pd}}}}\,.$$

This equation indicates that as pull-downs are added in series to form NAND gate inputs, the pull-up length must be enlarged to hold the logic threshold voltage constant.

The logic threshold voltage of an *n*-input NAND gate, assuming all the pulldowns have equal geometries, is

$$V_{\rm thNAND} \approx \frac{\rm VDD}{\sqrt{\frac{L_{\rm pu}/W_{\rm pu}}{nL_{\rm pd}/W_{\rm pd}}}}.$$

As inputs are added and pull-up length is increased, the delay time of the NAND gate is also correspondingly increased, for both rising and falling transitions:

$$\tau_{\rm NAND} \approx n \ \tau_{\rm inv}$$

.

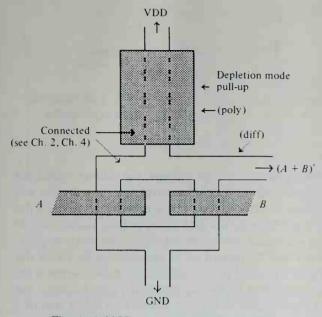

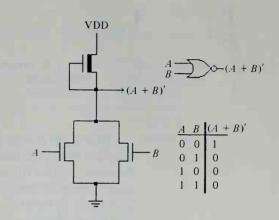

The circuit layout diagram of a two-input NOR gate is shown in Fig. 1.19. The layout is that of a basic inverter with an additional enhancement mode transistor in parallel with the pull-down transistor. Additional inputs may be constructed by simply placing more transistors in parallel with the pull-down path. The circuit diagram, truth table, and logic symbol for the two-input NOR gate are shown in Fig. 1.20. If either of the inputs A or B is a logic-1, the pull-down path to ground is closed and the output will be low and therefore a logic-0. For the output to be driven high, to logic-1, both inputs must be low, at logic-0. If one of its inputs is kept at logic-0, and the other swings between logic-0 and logic-1, the logic threshold voltage of the NOR gate is the same as that of a basic inverter of equal pull-up to pull-down ratio. If this ratio were 4:1 to provide equal margins, then  $V_{\text{thNOR}} \approx \text{VDD}/2$  with only one input active. However, if both pull-downs had equal geometries, and if both inputs were to move together between logic-0 and logic-0 and logic-1,  $V_{\text{thNOR}}$  would be reduced to  $\approx \text{VDD}/(8)^{1/2}$ . The logic threshold voltage of an

Fig. 1.19 NOR gate, top view of layout.

*n*-input NOR circuit decreases as a function of the number of active inputs (inputs moving together from logic-0 to logic-1). The delay time of the NOR gate with one input active is the same as that of an inverter of equal transistor geometries, except for added stray capacitance. Its delay time for falling transitions is decreased as more of its inputs are active.

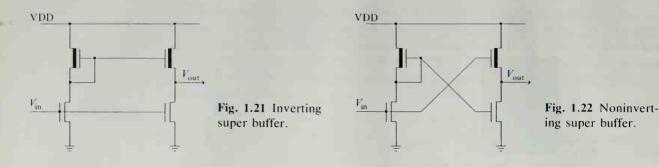

# 1.8 SUPER BUFFERS

As we have noted, ratio-type logic suffers from an asymmetry in its ability to drive capacitive loads. This asymmetry results from the fact that the pull-up transistor has of necessity less driving capability than the pull-down transistor. There are, however, methods for avoiding this asymmetry. Shown in Figs. 1.21 and 1.22 are circuits for both inverting and noninverting drivers that are approximately symmetrical in their capability of sourcing (sinking) charge into a capacitive load. Drivers of this type are called *super buffers*.

Both types of super buffer are built using a depletion mode pull-up transistor and an enhancement mode pull-down transistor, with a ratio of Z's of approximately 4:1 as in the basic inverter. However, the gate of the pull-up transistor, rather than being tied to its source, is tied to a signal that is the complement of that driving the pull-down transistor.

When the pull-down transistor gate is at a high voltage, the pull-up transistor gate will be approximately at ground, and the current through the super buffer will be similar to that through a standard inverter of the same size. However, when the gate of the pull-down transistor is put to zero, the gate of the pull-up transistor will go rapidly to VDD since it is the only load on the output of the previous inverter, and the depletion mode transistor will be turned on at approximately twice the drive it would experience if its gate were tied to its source. Since the current from a device in saturation goes approximately as the square of the gate voltage, the current-sourcing capability of a super buffer is approximately four times that of a standard inverter. Hence, the current-sourcing capability of its pull-ups is approximately equal to the current-sinking capability of its pull-downs, and waveforms from super buffers driving capacitive loads are nearly symmetrical.

The effective delay time,  $\tau$ , of super buffers is thus reduced to approximately the same value for high-going and low-going waveforms. Needless to say, when large capacitive loads are to be driven, super buffers are universally used. The arguments used in the last section to determine how many stages are used to drive a large capacitive load from a small source apply directly to super buffers. For that reason we have not explicitly indicated an inverter-ratio k in that section.

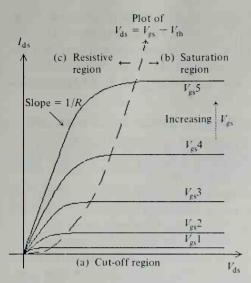

#### 1.9 A CLOSER LOOK AT THE ELECTRICAL PARAMETERS

Up to this point we have talked in very simple terms about the properties of the MOS transistors. They have a capacitance associated with their gate input and a transit time for electrons to move from the source to the drain. We have given simple expressions for the drain-to-source current. For very low  $V_{\rm ds}$ , the MOS transistor's drain-to-source path acts as a resistor whose conductance is directly proportional to the gate voltage above threshold, as given in Eq. (1–3). For values of  $V_{\rm ds}$  larger than  $V_{\rm gs} - V_{\rm th}$ , the device acts as a current source, with a current proportional to  $(V_{\rm gs} - V_{\rm th})^2$ , as given in Eq. (1–6). As  $V_{\rm ds}$  passes through the intermediate range between these two extremes, there is a smooth transition between the two types of behavior,<sup>3</sup> as given in the following equation:

$$I_{\rm ds} = \frac{Q}{\tau} = \frac{\mu C_{\rm g}}{L^2} \left[ (V_{\rm gs} - V_{\rm th}) V_{\rm ds} - \frac{V_{\rm ds}^2}{2} \right] . \tag{1-11}$$

**Fig. 1.23** Summary of MOS transistor characteristics. (a) Cut-off region:  $V_{gs} < V_{th}$ ,  $I_{ds} = 0$ . (b) Saturation region:  $V_{gs} \ge V_{th}$ .  $V_{ds}$  sufficiently high so  $V_{gd} < V_{th}$ , that is,  $V_{ds} \ge (V_{gs} - V_{th})$ . MOSFET acts as current source, with  $I_{ds}$  proportional to  $(V_{gs} - V_{th})^2$ . (c) Resistive region:  $V_{gs} \ge V_{th}$ .  $V_{ds}$  sufficiently low so  $V_{gd} \ge V_{th}$ , that is,  $V_{ds} < (V_{gs} - V_{th})$ . MOSFET acts as resistor, with resistance inversely proportional to  $(V_{gs} - V_{th})$ .

Figure 1.23 plots  $I_{ds}$  versus  $V_{ds}$ , summarizing the various regions of MOS transistor operation.

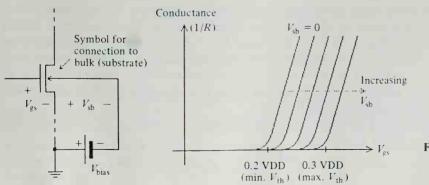

There is another electrical characteristic we may occasionally have to take into account. The threshold voltage of an MOS transistor is not a constant; it varies slightly as a function of the voltage between the source terminal of the transistor and the silicon substrate. This is called the *body effect* and it is illustrated in Fig. 1.24. The silicon substrate is usually connected to our system's circuit ground during packaging. However, a fixed bias voltage is sometimes applied between circuit ground and substrate as shown in Fig. 1.24, and this bias must be taken into account in estimating the body effect. If the source-to-bulk (substrate) voltage,  $V_{sb}$ , equals zero, then  $V_{th}$  is at its minimum value of approximately 0.2 VDD. As  $V_{sb}$  is increased,  $V_{th}$  increases slightly.

For enhancement mode transistors fabricated using typical processes,  $V_{\text{th}}$  reaches a maximum value of about 0.3 VDD when  $V_{\text{sh}}$  is increased to  $\approx$  VDD. The

Fig. 1.24 The body effect.

value of the depletion mode transistor threshold,  $V_{dep}$ , is similarly affected, ranging from about -0.8 VDD to -0.7 VDD as  $V_{sb}$  is raised from zero to VDD volts. As shown in Fig. 1.24, it is possible to insert a fixed bias voltage between the circuit ground and the substrate, rather than just connect them. Such a *substrate bias* provides an electrical mechanism for setting the threshold to an appropriate value.

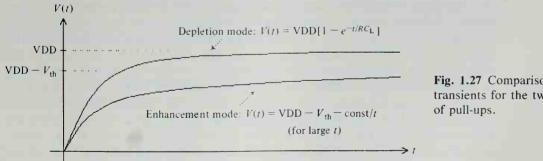

#### 1.10 DEPLETION MODE PULL-UPS VERSUS ENHANCEMENT MODE PULL-UPS

With its gate tied to VDD, an enhancement mode transistor will be on for all  $V_{ds} > V_{th}$ , and thus can be used for a pull-up device in inverting logic circuits. Early MOS processes used pull-up devices of exactly this type.

In this section we will make a comparison of the rising transients of the two types of pull-up circuits. As noted earlier, rising transients in ratio-type logic are usually slower than falling transients, and thus rising transients generally have greater impact on system performance. In the simplest cases, this asymmetry in the transients results from the current-sourcing capability of the pull-up transistor being less than that of its pull-down counterpart. The simple intuitive time arguments given earlier are quite adequate for making estimates of system performance in most cases. However, there are situations in which the transient time may be much longer than a naive estimate would indicate. The rising transient of the enhancement mode pull-up is one of these.

A depletion mode pull-up transistor feeding a capacitive load is shown schematically in Fig. 1.25. Since  $V_{gs} \ge V_{th}$  and  $V_{gd} \ge V_{th}$ , the pull-up transistor is in the resistive region. The final stages of the rising transient are given by the following exponential:

$$V(t) = VDD[1 - e^{-t/(RC_L)}]$$

.

For an inverter-ratio k, pull-down transit time  $\tau$ , and gate capacitance  $C_g$ , the time-constant of the rising transient is given by

$$RC_{\rm L} = k\tau \frac{C_{\rm L}}{C_{\rm g}}$$

A somewhat more complicated situation is presented by an enhancement mode transistor sourcing charge into a capacitive load. This situation is shown schematically in Fig. 1.26. Note that since  $V_{gd} = 0$ , the transistor is in saturation whenever  $V_{gs} > V_{th}$ . The problem with sourcing charge from the enhancement mode transistor is that as the voltage at the output node gets closer and closer to one threshold below VDD, the amount of current provided by the enhancement mode transistor decreases rapidly.

The dependence of the enhancement mode pull-up current,  $I_{ds}$ , on output voltage, V, is given in Eq. (1–12):

$$Q = -\frac{\epsilon WL}{D} \left[ (VDD - V_{th}) - V \right];$$

Fig. 1.25 Depletion mode MOSFET pulling up a capacitive load.

**Fig. 1.26** Enhancement mode MOSFET pulling up a capacitive load.

$$\tau = \frac{2L^2}{\mu[(VDD - V_{th}) - V]};$$

$$I_{ds} = -\frac{Q}{\tau} = \frac{\mu \epsilon W}{2LD} [(VDD - V_{th}) - V]^2.$$

(1-12)

The fact that the pull-up current decreases as the output voltage nears its maximum value causes the rising transient from such a circuit to be of qualitatively different form than that of a depletion mode pull-up. Equating  $I_{ds} = C_L dV/dt$ with the expression in Eq. (1-12), and then solving for V(t), we find the rising voltage transient, for large t:

$$V(t) = \text{VDD} - V_{\text{th}'} - C_{\text{L}} \frac{LD}{\mu \epsilon W t} \quad . \tag{1-13}$$

Note that in this configuration, the threshold voltage  $V_{\text{th}'}$  of the pull-up is near its maximum value as V(t) rises towards VDD, due to the body effect.

A comparison of the rising transients of the preceding two circuits, assuming the same load capacitance and the same pull-up source current at zero output voltage, is shown in Fig. 1.27. The rising transient for the depletion mode pull-up transistor is crisp and converges rapidly towards VDD. However, the rising transignt for the enhancement mode pull-up transistor, while starting rapidly, lags far behind, and within the expected time response of the system it never even comes close to one threshold below VDD. Even for very large t,  $V(t) < VDD - V_{th'}$ .

Fig. 1.27 Comparisons of rising transients for the two types

The practical effect of this property of enhancement mode transistors is that circuits designed to work from the output of such a circuit should be designed with an inverter threshold  $V_{inv}$  considerably lower than that of circuits designed to work with the output of a depletion mode pull-up circuit. In order to obtain equal inverter margins without sacrificing performance, we will normally use depletion mode pull-ups.

#### 1.11 DELAYS IN ANOTHER FORM OF LOGIC CIRCUITRY

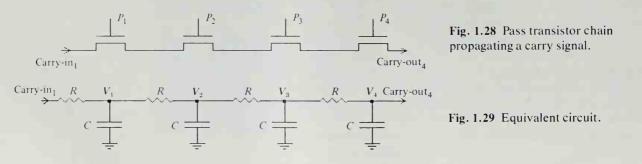

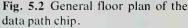

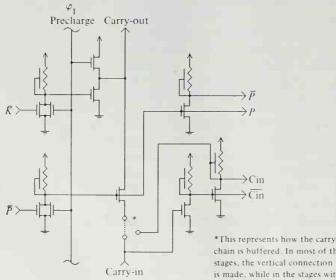

Enhancement mode transistors, when used in small numbers and driving small capacitive loads, may often be used as switches in circuits of simple topology to provide logic-signal steering functions of much greater complexity than could be easily achieved in ratio-type inverting logic. These circuits are reminiscent of relay-switching logic, and transistors used in this way are referred to as "pass transistors" or "transmission gates." Examples of circuits using this type of design are given in Chapter 3. A particularly interesting example is the Manchester carry chain,<sup>5.6</sup> used for propagating carry signals in parallel adders. In each stage of the adder, a carry-propagate signal is derived from the two input variables to the adder, and if it is desired to propagate the carry, this propagate signal is applied to the gate of an enhancement mode pass transistor. The source of the transistor is "carry-in" to the present stage, and the drain of the transistor is "carry-out" to the next stage. In this way, a carry can be propagated from less significant to more significant stages of the adder without inserting a full inverter delay between stages. The circuit is shown schematically in Fig. 1.28.

The delay through such a circuit does not involve inverter delays but is of an entirely different sort. A voltage along the chain divides into  $V_{ds}$  across each pass transistor. Thus  $V_{ds}$  is usually low, and the pass transistors operate primarily in the resistive region. We can think of each transistor as (1) a series resistance in the carry path, (2) a capacitance to ground formed by the gate-to-channel capacitance of each transistor, and (3) the strays associated with the source, drain, and connections with the following stage. An abstraction of the electrical representation is shown in Fig. 1.29. The minimum value of R is the turned-on resistance of each enhancement mode pass transistor, while the minimum value of C is the capacitance from gate to channel of the pass transistor. Strays will increase both values, especially that of C. The response at the node labeled  $V_2$  with respect to time is given in Eq. (1–14). In the limit as the number of sections in the network becomes large, Eq. (1–14) reduces to the differential form shown in Eq. (1–15), where R and C are now the resistance and capacitance per unit length, respectively.

$$C \, dV_2/dt = [(V_1 - V_2) - (V_2 - V_3)]/R \tag{1-14}$$

$RC \ dV/dt = d^2 V/dx^2 \tag{1-15}$

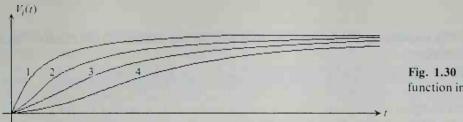

Equation (1-15) is the well-known diffusion equation, and while its solutions are complex, in general the time required for a transient to propagate a distance x in such a system is proportional to  $x^2$ . One can see qualitatively that this might be so. Doubling the number of sections in such a network doubles both the resistance and the capacitance and therefore causes the time required for the system to respond to increase by a factor of approximately four. The response of a system of n stages to a step function input is shown in Fig. 1.30.

If we add one more pass transistor to such a chain of n pass transistors, the added delay through the chain is small for small n but very large for large n. Therefore, it is highly desirable to group the pass transistors used for steering logic, multiplexing logic, and carry-chain-type logic into short sections and interpose inverting logic between these sections. This approach applied to the carry chain is shown in Fig. 1.31, where an inverter is inserted after every n pass transistors. The delay through a section of n pass transistors is proportional to  $RCn^2$ . Thus the total delay through one section is approximately  $RCn^2$  plus the delay through the inverter  $\tau_{inv}$ :

$$\approx RCn^2 + \tau_{inv}$$

The average delay per pass transistor stage is

$$\approx RCn + \tau_{\rm inv}/n. \tag{1-16}$$

To minimize the delay per stage, we choose n such that the delay through n pass transistors equals the inverter delay:

$$RCn^2 \approx \tau_{\rm inv}.$$

Since logic done by steering signals with pass transistors does not require static power dissipation, a generalization of this result may be formulated. It pays to put as much logic into steering-type circuits as possible until there are enough pass transistors to delay the signal by approximately one inverting logic delay. At this point, the level of the signal can be restored by an inverting logic stage.

Fig. 1.31 Minimizing delay by interposing inverters.

The pass transistor has another important advantage over an inverting logic stage. When used to control or steer a logic signal, the pass transistor has only one input, one control, and one output connection. A NAND or NOR logic gate implementing the same function, in addition to containing two more transistors and thus occupying more area, also requires VDD and GND connections. As a result, the topology of interconnection of pass transistor circuits is far simpler than that of inverting-logic circuits. The topological simplicity of pass transistor control gates is an important factor in the system-design concepts developed in later chapters.

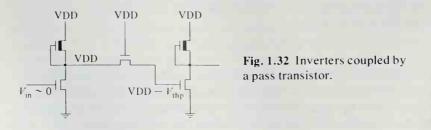

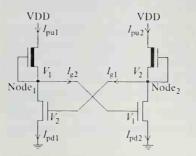

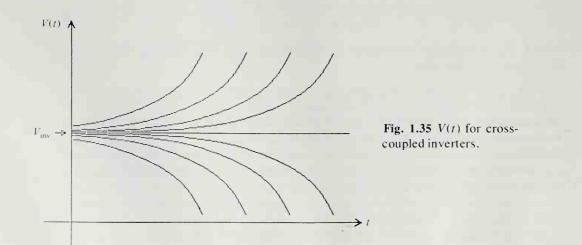

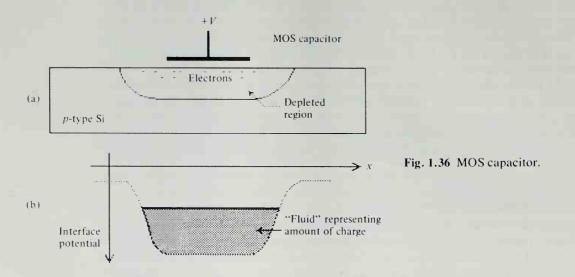

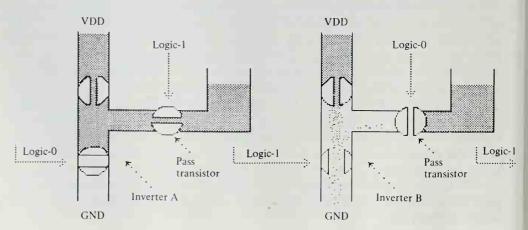

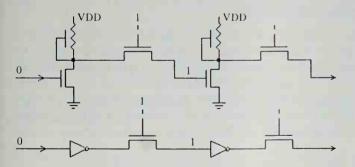

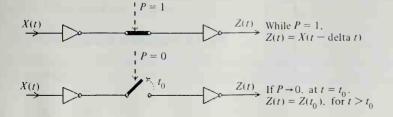

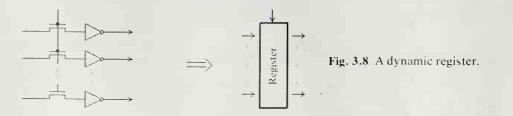

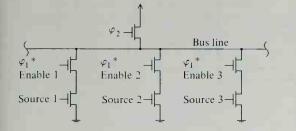

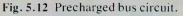

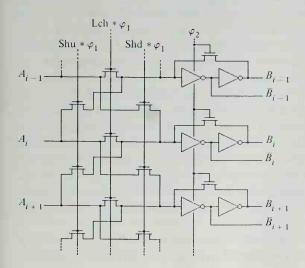

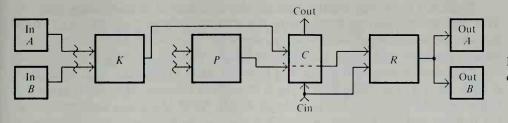

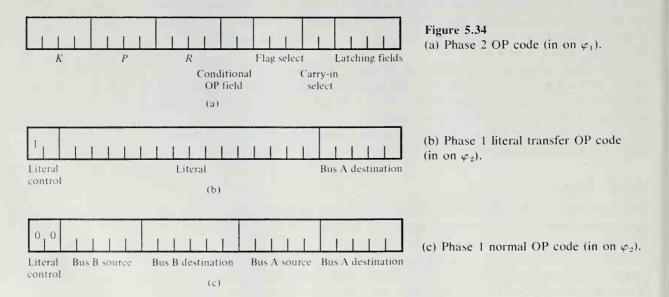

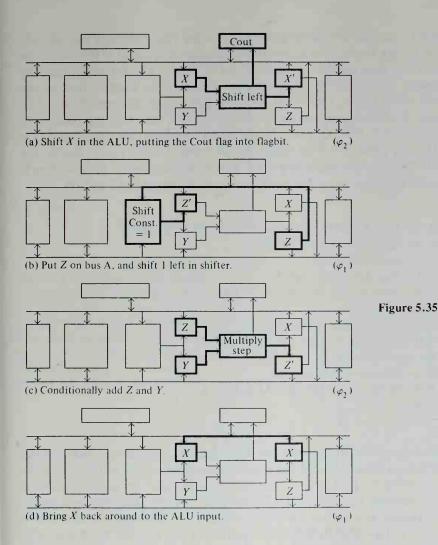

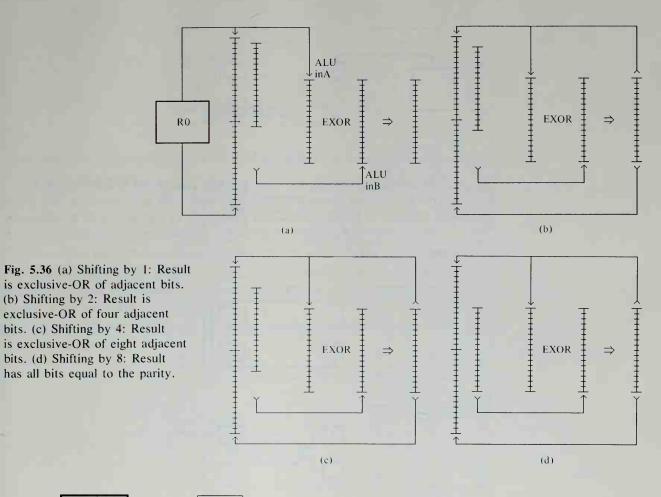

# 1.12 PULL-UP/PULL-DOWN RATIOS FOR INVERTING LOGIC COUPLED BY PASS TRANSISTORS